### S3 Family 8-Bit Microcontrollers

## S3F80PB MCU

## **Product Specification**

PS032103-0815

PRELIMINARY

Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2015 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

S3 and Z8 are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                               |

|-------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Aug<br>2015 | 03                | Replaced Figure 4. Pin Assignments, 32-Pin ELP Package with updated pinout, updated Table 1. Pin Descriptions, 32-Pin SOP/ELP Packages.                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>7, 8</u>                                        |

| Dec<br>2014 | 02                | Added pin assignments for the 32-pin ELP and 44-pin ELP packages (Figures 4 and 5); modified Tables 1 and 2 to include pin descriptions for the 32-pin and 44-pin ELP packages; modified pin circuit diagrams, Figures 6 through 11; modified Noncontiguous 16-Byte Working Register Block (Figure 19); modified Op Code Quick Reference (changed Irr to Ir in D2; CPIJNE, Table 26); corrected Figure 50 to imply hex values; modified D.C. Electrical Characteristics (Table 94); deleted Slew Rate of LVD data from Low Voltage Detect Circuit (Table 96); updated to Zilog style. | 7, 10,<br>13–18,<br>29, 91,<br>151,<br>300,<br>302 |

| Mar<br>2014 | 01                | Original Zilog issue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | All                                                |

## **Table of Contents**

| Revision H   | istory | 'iii                                                           |

|--------------|--------|----------------------------------------------------------------|

| List of Figu | ires . | xi                                                             |

| List of Tabl | les    | xiv                                                            |

| Chapter 1.   | Ove    | rview 1                                                        |

|              | 1.1.   | S3F80PB Microcontroller                                        |

|              | 1.2.   | Features                                                       |

|              | 1.3.   | Block Diagram 4                                                |

|              | 1.4.   | Pin Assignments                                                |

|              | 1.5.   | Pin Circuits                                                   |

| Chapter 2.   | Add    | ress Space                                                     |

|              | 2.1.   | Program Memory                                                 |

|              |        | 2.1.1. Smart Option                                            |

|              | 2.2.   | Register Architecture                                          |

|              |        | 2.2.1. Register Page Pointer                                   |

|              |        | 2.2.2. Register Set1                                           |

|              |        | 2.2.3. Register Set2                                           |

|              |        | 2.2.4. Prime Register Space                                    |

|              |        | 2.2.5. Working Registers282.2.6. Using the Register Pointers29 |

|              | 2.3    | Register Addressing                                            |

|              | 2.3.   | 2.3.1. Common Working Register Area                            |

|              |        | 2.3.2. 4-Bit Working Register Addressing                       |

|              |        | 2.3.3. 8-Bit Working Register Addressing                       |

|              | 2.4.   | Register Pointer Registers                                     |

|              |        | System and User Stacks                                         |

|              |        | 2.5.1. Stack Operations                                        |

|              |        | 2.5.2. User-Defined Stacks                                     |

|              |        | 2.5.3. Stack Pointers                                          |

|              | 2.6.   | Stack Pointer Register                                         |

| Chapter 3.   | Add    | ressing Modes                                                  |

|              | 3.1.   | Register Addressing Mode                                       |

|              | 3.2.   | Indirect Register Addressing Mode                              |

|              | 3.3.   | Indexed Addressing Mode                                        |

|              | 3.4.   | Direct Address Mode                                            |

| UU          |   |

|-------------|---|

| lad In Life |   |

| Camana      | ı |

|            | 3.5. Indirect Address Mode                       |

|------------|--------------------------------------------------|

|            | 3.6. Relative Address Mode                       |

|            | 3.7. Immediate Mode                              |

| Chapter 4. | Control Registers                                |

| •          | 4.1. External Memory Timing Register             |

| Chapter 5. | Interrupt Structure                              |

|            | 5.1. Levels                                      |

|            | 5.2. Vectors                                     |

|            | 5.3. Sources                                     |

|            | 5.4. Interrupt Types                             |

|            | 5.5. Interrupt Vector Addresses                  |

|            | 5.6. Enable/Disable Interrupt Instructions       |

|            | 5.7. Interrupt Processing Control Points         |

|            | 5.8. Peripheral Interrupt Control Registers      |

|            | 5.9. System Mode Register 7                      |

|            | 5.10. Interrupt Mask Register                    |

|            | 5.11. Interrupt Priority Register                |

|            | 5.12. Interrupt Request Register                 |

|            | 5.13. Interrupt Pending Function Types           |

|            | 5.14. Interrupt Source Polling Sequence          |

|            | 5.15. Interrupt Service Routines                 |

|            | 5.16. Generating Interrupt Vector Addresses      |

|            | 5.17. Nesting of Vectored Interrupts             |

|            | 5.18. Instruction Pointer                        |

|            | 5.19. Fast Interrupt Processing                  |

|            | 5.19.1. Procedure for Initiating Fast Interrupts |

|            | 5.19.2. Fast Interrupt Service Routine           |

|            | 5.19.3. Programming Guidelines                   |

| Chapter 6. | CPU Instructions                                 |

|            | 6.1. Data Types                                  |

|            | 6.2. Register Addressing                         |

|            | 6.3. Addressing Modes                            |

|            | 6.4. Instruction Summary                         |

|            | 6.5. Flags Register                              |

|            | 6.6 Instruction Set Notation 89                  |

| Chapter 7. | Op ( | Code Maps                                | . 91 |

|------------|------|------------------------------------------|------|

|            | 7.1. | Condition Codes                          | . 93 |

|            | 7.2. | Instruction Set                          | . 94 |

|            |      | Add with Carry                           | . 95 |

|            |      | Add                                      | . 97 |

|            |      | Logical AND                              | . 99 |

|            |      | BAND-Bit AND                             | 101  |

|            |      | Bit Compare                              | 102  |

|            |      | Bit Complement                           | 103  |

|            |      | Bit Reset                                | 104  |

|            |      | Bit Set                                  | 105  |

|            |      | Bit OR                                   | 106  |

|            |      | Bit Test, Jump Relative on False         |      |

|            |      | Bit Test, Jump Relative on True          |      |

|            |      | Bit XOR                                  |      |

|            |      | Call Procedure                           |      |

|            |      | Complement Carry Flag                    |      |

|            |      | Clear                                    |      |

|            |      | Complement                               |      |

|            |      | Compare                                  |      |

|            |      | Compare, Increment, and Jump on Equal    |      |

|            |      | Compare, Increment, and Jump on NonEqual |      |

|            |      | Decimal Adjust                           |      |

|            |      | Decrement                                |      |

|            |      | Decrement Word                           |      |

|            |      | Disable Interrupts                       |      |

|            |      | Divide (Unsigned)                        |      |

|            |      | Decrement and Jump if NonZero            |      |

|            |      | Enable Interrupts                        |      |

|            |      | Enter                                    |      |

|            |      | Exit                                     |      |

|            |      | Idle Operation                           |      |

|            |      | Increment                                |      |

|            |      | Increment Word                           |      |

|            |      | Interrupt Return                         |      |

|            |      | Jump                                     |      |

|            |      | Jump Relative                            |      |

|            |      | Load Did                                 |      |

|            |      | Load Marrows                             |      |

|            |      | Load Memory and Degrament                |      |

|            |      | Load Memory and Decrement                | 145  |

|      | Load Memory and Increment      | 6 |

|------|--------------------------------|---|

|      | Load Memory with PreDecrement  | 7 |

|      | Load Memory with PreIncrement  | 8 |

|      | Load Word                      |   |

|      | Multiply (Unsigned)            | 0 |

|      | Next                           | 1 |

|      | No Operation                   | 2 |

|      | Logical OR                     | 3 |

|      | Pop from Stack                 | 5 |

|      | Pop User Stack (Decrementing)  | 6 |

|      | Pop User Stack (Incrementing)  | 7 |

|      | Push to Stack                  | 8 |

|      | Push User Stack (Decrementing) | 9 |

|      | Push User Stack (Incrementing) | 0 |

|      | Reset Carry Flag               | 1 |

|      | Return                         | 2 |

|      | Rotate Left                    | 3 |

|      | Rotate Left through Carry      | 5 |

|      | Rotate Right                   | 7 |

|      | Rotate Right through Carry 169 | 9 |

|      | Select Bank0                   | 1 |

|      | Select Bank1                   | 2 |

|      | Subtract with Carry            |   |

|      | Set Carry Flag                 | 5 |

|      | Shift Right Arithmetic         | 6 |

|      | Set Register Pointer           | 8 |

|      | Stop Operation                 | 9 |

|      | Subtract                       | 0 |

|      | Swap Nibbles                   |   |

|      | Test Complement under Mask     |   |

|      | Test Under Mask                | 5 |

|      | Wait for Interrupt             |   |

|      | Logical Exclusive OR           | 8 |

| Cloc | k, Power, and Reset Circuits   | 0 |

| 8.1. | System Clock Circuit           | 0 |

| 8.2. | •                              |   |

|      | System Clock Control Register  |   |

|      | et                             |   |

|      |                                |   |

| 9 I  | Reset Sources 19               | ٦ |

Chapter 8.

Chapter 9.

|             | 9.2.  | Reset Mechanism                                          | 197 |

|-------------|-------|----------------------------------------------------------|-----|

|             | 9.3.  | External Reset Pin                                       | 198 |

|             | 9.4.  | Watchdog Timer Reset                                     | 198 |

|             | 9.5.  | LVD Reset                                                | 198 |

|             | 9.6.  | Internal Power-On Reset                                  | 199 |

|             | 9.7.  | External Interrupt Reset                                 | 200 |

|             | 9.8.  | Stop Error Detection & Recovery                          | 201 |

|             | 9.9.  | External Reset Pin                                       | 201 |

|             | 9.10. | . Power-Down Modes                                       | 201 |

|             |       | 9.10.1. Idle Mode                                        | 202 |

|             |       | 9.10.2. Idle Mode Release                                |     |

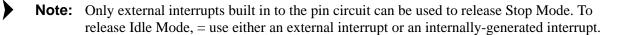

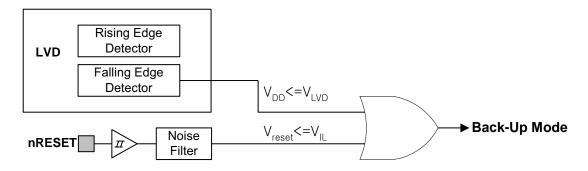

|             |       | 9.10.3. Backup Mode                                      |     |

|             |       | 9.10.4. Stop Mode                                        |     |

|             |       | 9.10.5. Sources to Release Stop Mode                     |     |

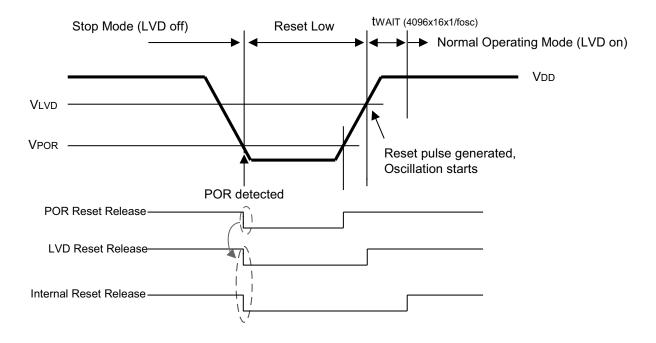

|             |       | 9.10.7. Using IPOR to Release Stop Mode                  |     |

|             |       | 9.10.8. Using an External Interrupt to Release Stop Mode |     |

|             |       | 9.10.9. Stop Error Detect and Recovery                   |     |

|             | 9.11. | . System Reset Operation                                 | 208 |

|             |       | 9.11.1. Hardware Reset Values                            | 209 |

|             | 9.12. | . Recommendation for Unused Pins                         | 214 |

|             | 9.13. | . Reset Source Indicating Register                       | 216 |

| Chapter 10. | I/O I | Ports                                                    | 217 |

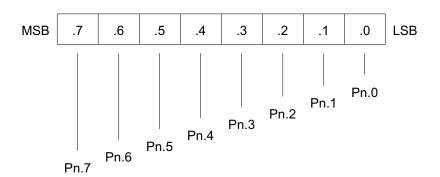

| _           | 10.1. | . Port Data Registers                                    | 218 |

|             |       | . Port 0                                                 |     |

|             |       | 10.2.1. Port 1                                           | 225 |

|             |       | 10.2.2. Port 2                                           |     |

|             | 10.3  | . Port 3                                                 | 236 |

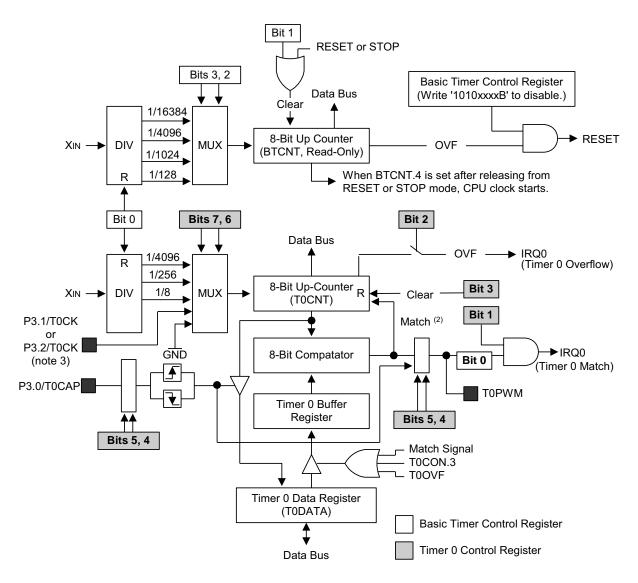

| Chapter 11. | Basic | c Timer and Timer 0                                      | 244 |

|             | 11.1. | . Basic Timer                                            | 245 |

|             | 11.2. | . Basic Timer Control Register                           | 246 |

|             | 11.3. | . Timer 0 Control Register                               | 248 |

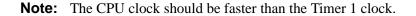

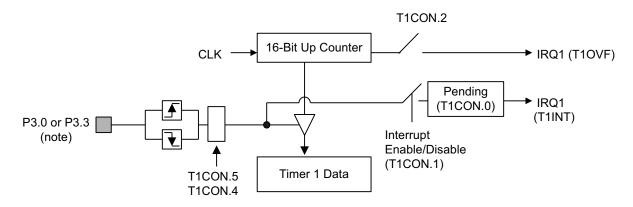

| Chapter 12. | Time  | er 1                                                     | 256 |

|             |       | . Timer 1 Control Register                               |     |

|             |       | . Timer 1 Overflow Interrupt                             |     |

|             |       | . Timer 1 Capture Interrupt                              |     |

|             |       | Timer 1 Match Interrupt                                  |     |

|             |       | <u>*</u>                                                 |     |

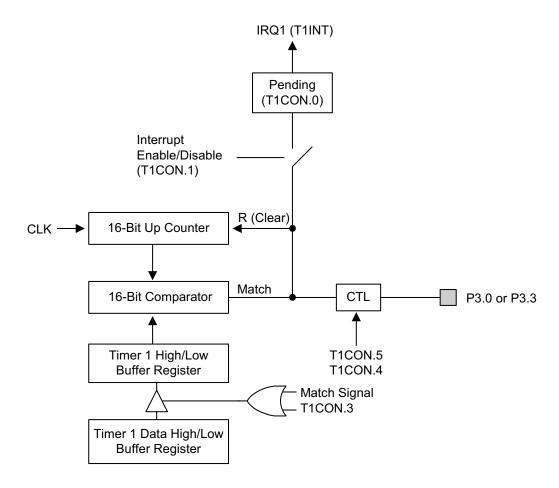

| Chapter 13. Counter A                                                      | 53 |

|----------------------------------------------------------------------------|----|

| 13.1. Counter A Control Register                                           |    |

| 13.1.1. Counter A Pulse Width Calculations                                 | 56 |

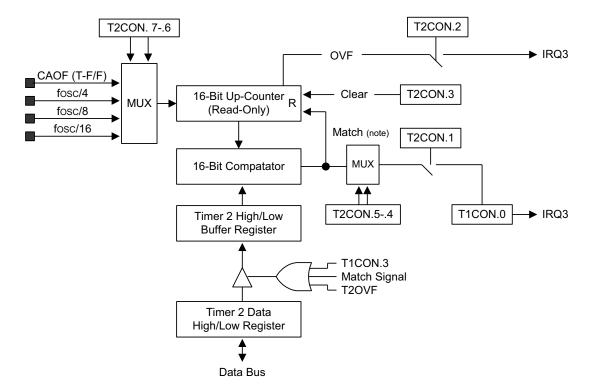

| Chapter 14. Timer 2                                                        | 70 |

| 14.1. Timer 2 Control Register                                             | 72 |

| 14.2. Timer 2 Overflow Interrupt                                           | 74 |

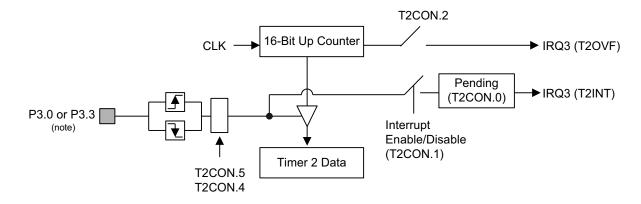

| 14.3. Timer 2 Capture Interrupt                                            | 74 |

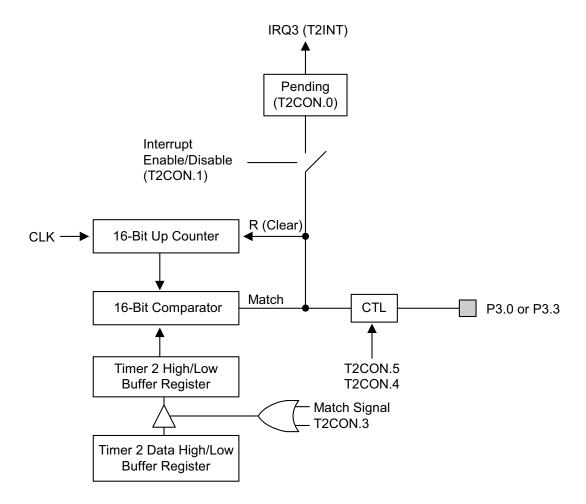

| 14.4. Timer 2 Match Interrupt                                              | 75 |

| Chapter 15. Embedded Flash Memory Interface                                | 77 |

| 15.1. Flash ROM Configuration                                              | 77 |

| 15.2. User Program Mode                                                    | 78 |

| 15.3. ISP On-Board Programming Sector                                      | 78 |

| 15.4. ISP Reset Vector and ISP Sector Size                                 | 30 |

| 15.5. Flash Memory Control Registers                                       |    |

| 15.5.1. Flash Memory User Programming Enable Register 28                   |    |

| 15.5.2. Flash Memory Sector Address Registers                              |    |

| 15.6. Sector Erase Operations                                              |    |

| 15.7. Program Operations                                                   |    |

| 15.8. Read Operations                                                      |    |

| 15.8.1. Hard Lock Protection                                               |    |

|                                                                            |    |

| Chapter 16. Low Voltage Detection       29         16.1. LVD Flag       29 |    |

| 16.2. Low Voltage Detection Control Register                               |    |

| 16.3. Low Voltage Detection Flag Selection Register                        |    |

|                                                                            |    |

| Chapter 17. Electrical Characteristics                                     |    |

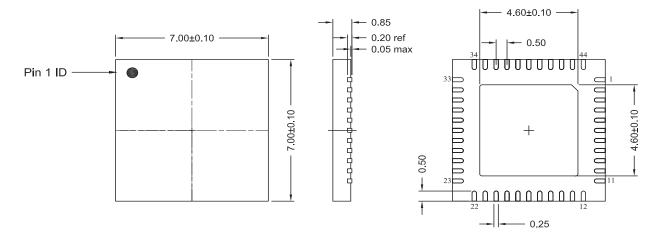

| Chapter 18. Mechanical Data                                                | )9 |

| Chapter 19. Flash Programming                                              | 13 |

| 19.1. Test Pin Voltage                                                     | 14 |

| 19.2. Operating Mode Characteristics                                       | 14 |

| Chapter 20. Development Tools                                              | 15 |

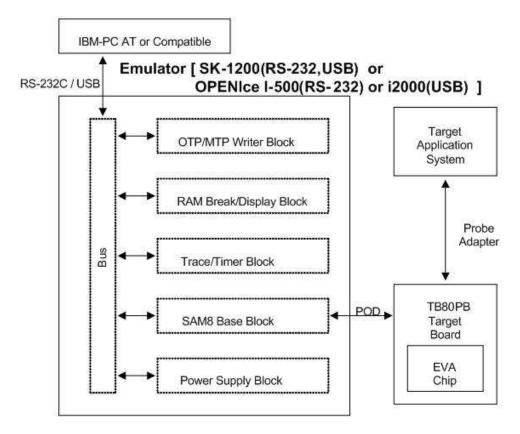

| 20.1. Development System Configuration                                     | 15 |

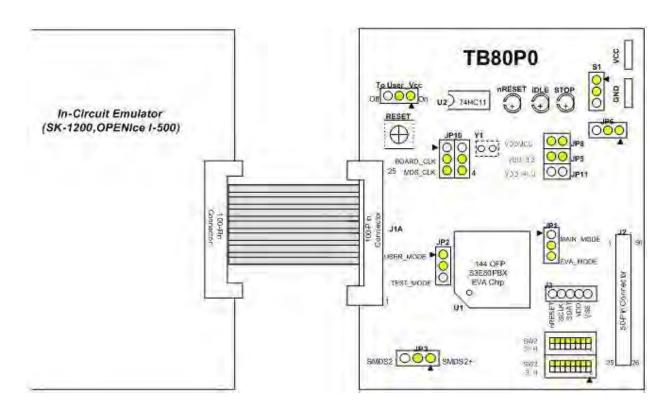

| 20.2. TB80PB Target Board                                                  | 16 |

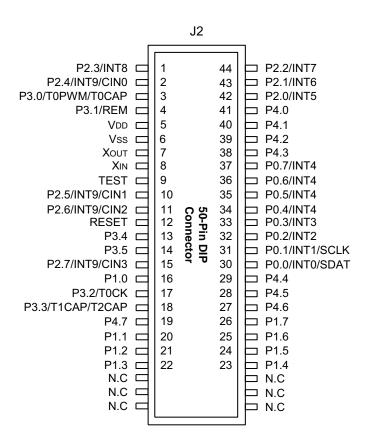

| 20.3. Probe Adapter                                                        | 20 |

| 20.4. Third Parties for Development Tools                                  | 20 |

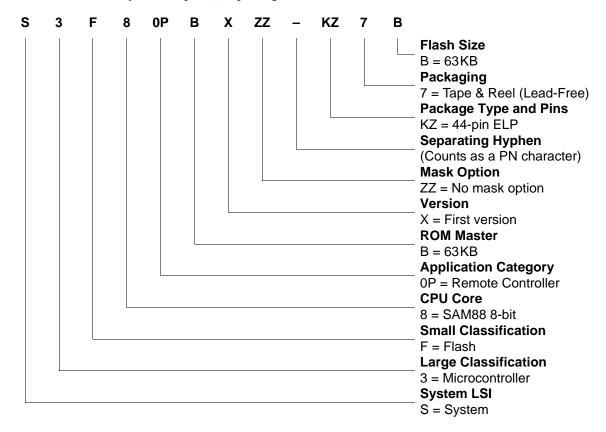

| Chapter 21. Ordering Information        | 321 |

|-----------------------------------------|-----|

| 21.0.1. Part Number Suffix Designations | 321 |

| Customer Support                        | 322 |

# List of Figures

| Figure 1.  | 32-Pin SOP/ELP Block Diagram                           | 4    |

|------------|--------------------------------------------------------|------|

| Figure 2.  | 44-Pin QFP/ELP Block Diagram                           | 5    |

| Figure 3.  | Pin Assignments, 32-Pin SOP Package                    | 6    |

| Figure 4.  | Pin Assignments, 32-Pin ELP Package                    | 7    |

| Figure 5.  | Pin Assignments, 44-Pin QFP and ELP Packages           | . 10 |

| Figure 6.  | Port 0 Pin Circuit, Type 1                             | . 13 |

| Figure 7.  | Port 1, Port 4, P3.4 and P3.5 Pin Circuit, Type 2      | . 14 |

| Figure 8.  | Port 2 Pin Circuit, Type 3                             | . 15 |

| Figure 9.  | Port 3.0 Pin Circuit, Type 4                           | . 16 |

| Figure 10. | P3.1 Pin Circuit, Type 5                               | . 17 |

| Figure 11. | P3.2 and P3.3 Pin Circuit, Type 6                      | . 18 |

| Figure 12. | nRESET Pin Circuit, Type 7                             | . 18 |

| Figure 13. | Program Memory Address Space                           | . 20 |

| Figure 14. | Smart Option                                           | . 22 |

| Figure 15. | Internal Register File Organization                    | . 25 |

| Figure 16. | Set1, Set2, and Prime Area Register Map                | . 27 |

| Figure 17. | 8-Byte Working Register Areas                          | . 28 |

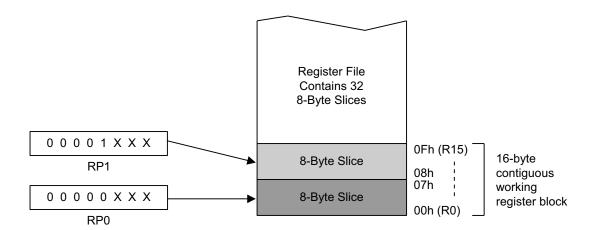

| Figure 18. | Contiguous 16-Byte Working Register Block              | . 29 |

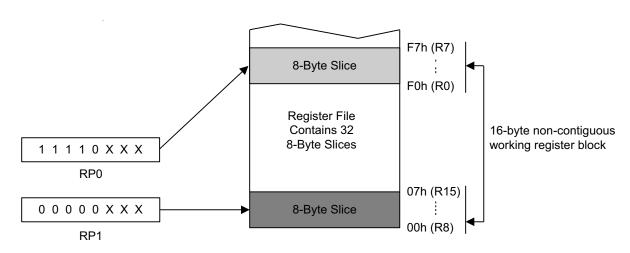

| Figure 19. | Noncontiguous 16-Byte Working Register Block           | . 29 |

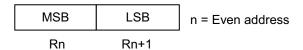

| Figure 20. | 16-Bit Register Pair                                   | . 31 |

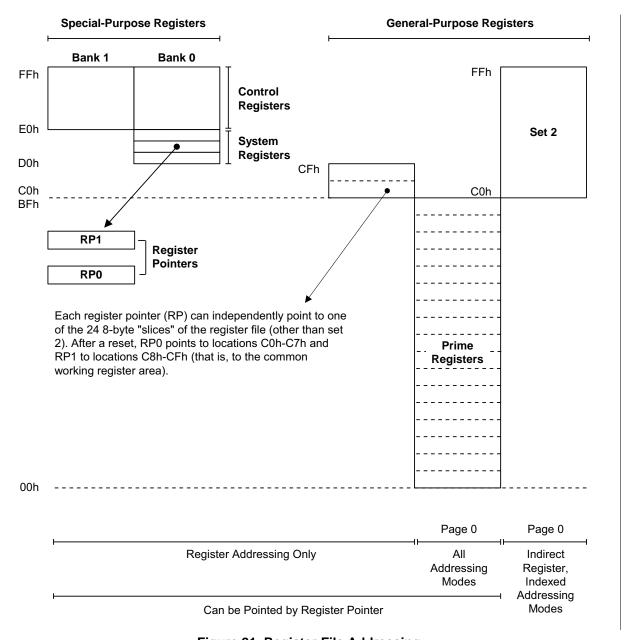

| Figure 21. | Register File Addressing                               | . 32 |

| Figure 22. | Common Working Register Area                           | . 33 |

| Figure 23. | 4-Bit Working Register Addressing                      | . 35 |

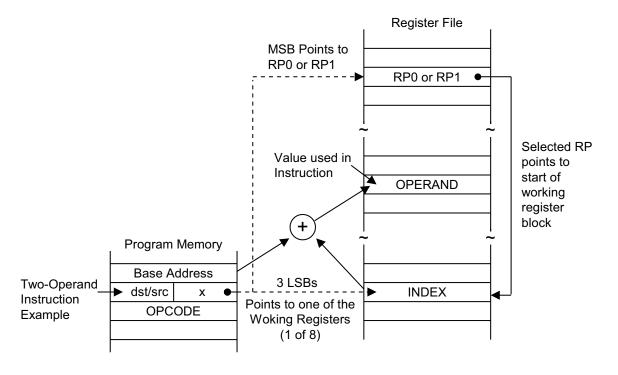

| Figure 24. | 4-Bit Working Register Addressing Example              | . 36 |

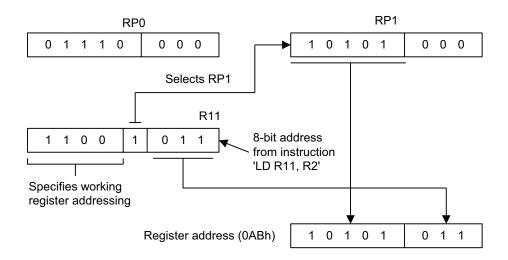

| Figure 25. | 8-Bit Working Register Addressing                      | . 37 |

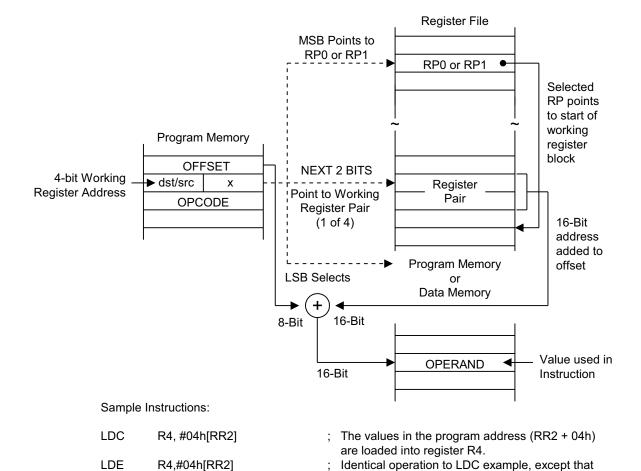

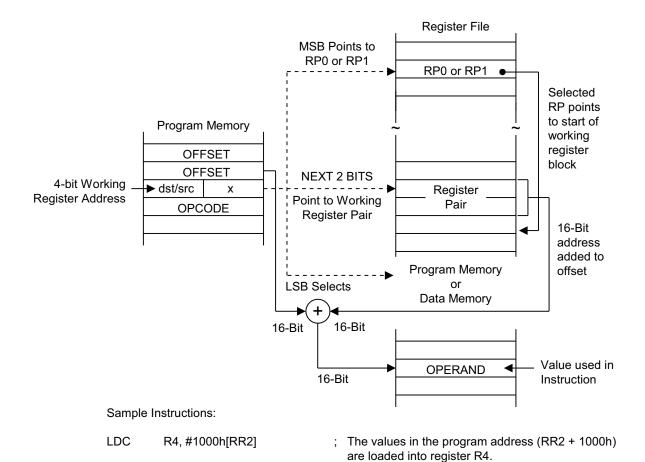

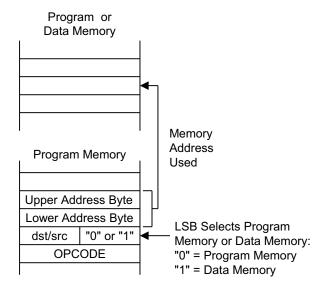

| Figure 26. | 8-Bit Working Register Addressing Example              | . 38 |

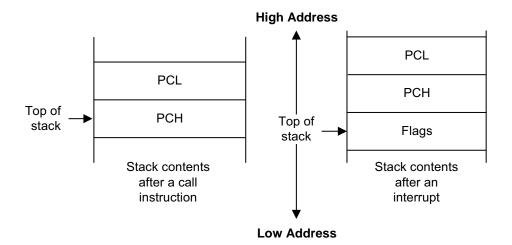

| Figure 27. | Stack Operations                                       | . 40 |

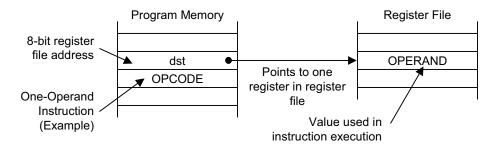

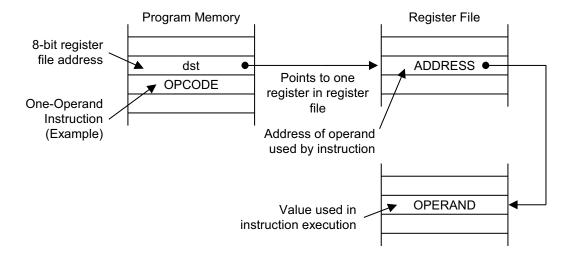

| Figure 28. | Register Addressing                                    | . 44 |

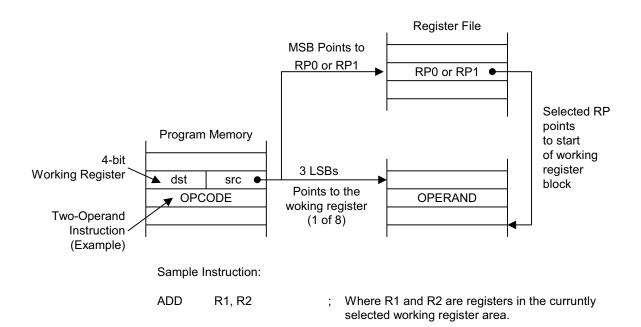

| Figure 29. | Working Register Addressing                            | . 44 |

| Figure 30. | Indirect Register Addressing to Register File          | . 45 |

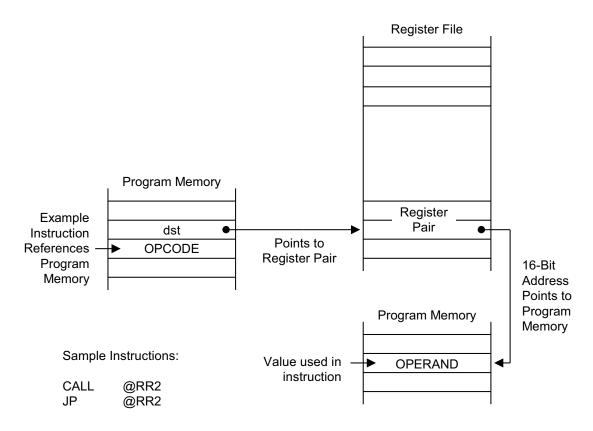

| Figure 31. | Indirect Register Addressing to Program Memory         | . 46 |

| Figure 32. | Indirect Register Addressing to Register File          | . 47 |

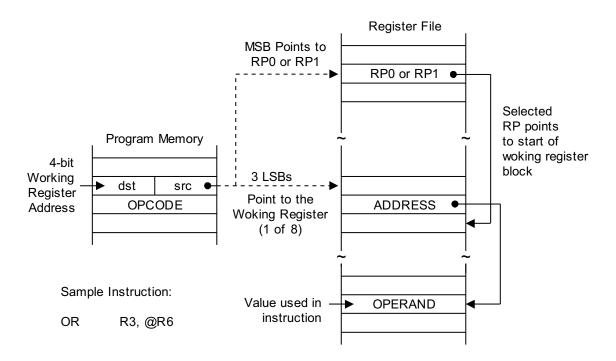

| Figure 33. | Indirect Register Addressing to Program or Data Memory | . 48 |

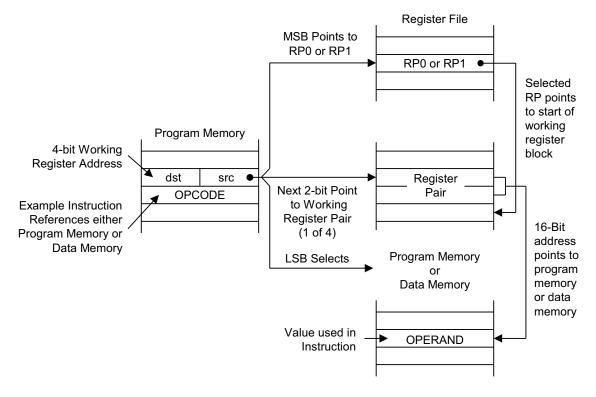

| Figure 34. | Indexed Addressing to Register File                    | . 49 |

| Figure 35. | Indexed Addressing to Program or Data Memory with Short Offset  | 50    |

|------------|-----------------------------------------------------------------|-------|

| Figure 36. | Indexed Addressing to Program or Data Memory                    | 51    |

| Figure 37. | Direct Addressing for Load Instructions                         | 52    |

| Figure 38. | Direct Addressing for Call and Jump Instructions                | 53    |

| Figure 39. | Indirect Addressing                                             | 54    |

| Figure 40. | Relative Addressing                                             | 55    |

| Figure 41. | Immediate Addressing                                            | 56    |

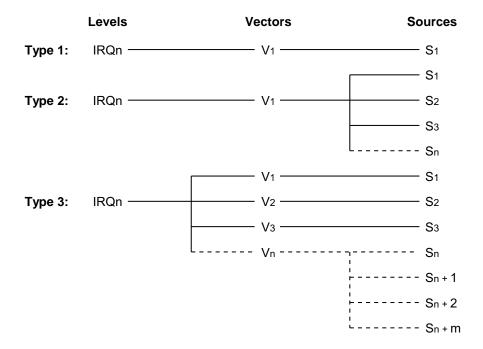

| Figure 42. | S3 Family Interrupt Types                                       | 62    |

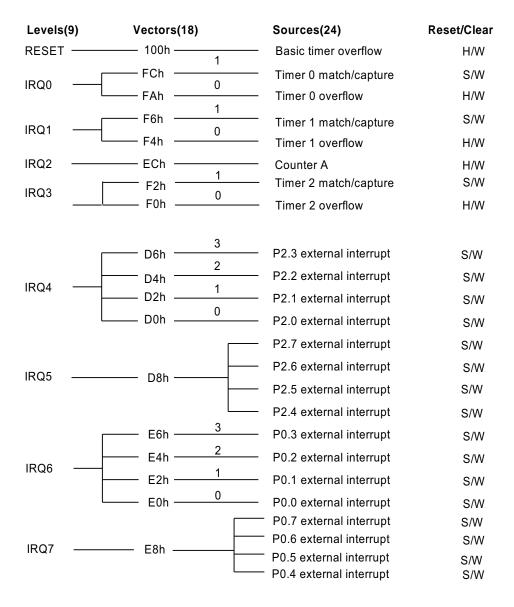

| Figure 43. | S3F80PB Interrupt Structure                                     | 64    |

| Figure 44. | ROM Vector Address Area                                         | 65    |

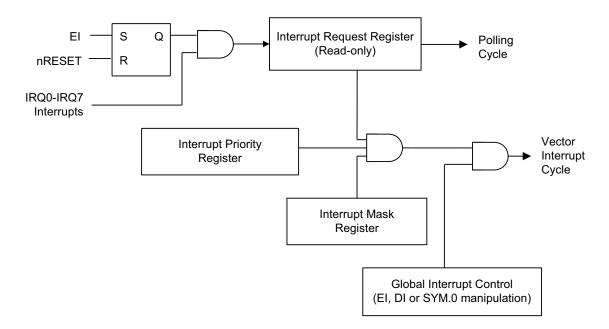

| Figure 45. | Interrupt Function Diagram                                      | 69    |

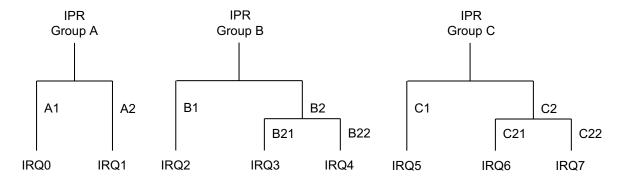

| Figure 46. | Interrupt Request Priority Groups                               | 74    |

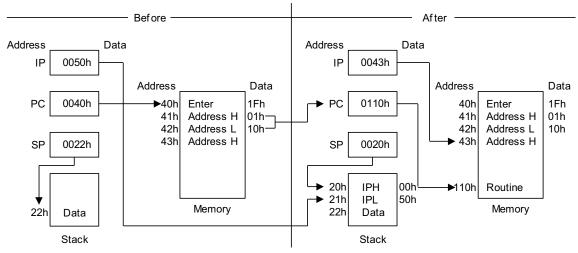

| Figure 47. | How to Use an ENTER Statement                                   | . 129 |

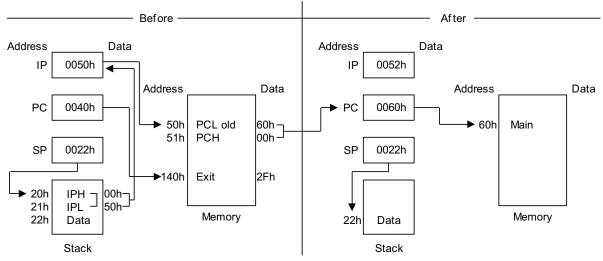

| Figure 48. | How to Use an EXIT Statement                                    | . 130 |

| Figure 49. | Instruction Pointer                                             | . 136 |

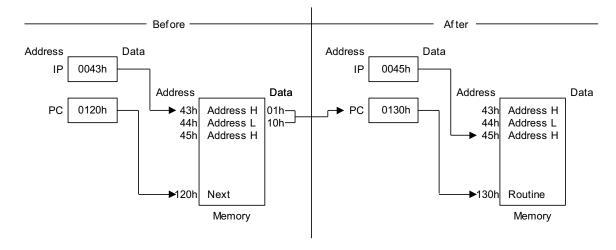

| Figure 50. | How to Use the NEXT Instruction                                 | . 151 |

| Figure 51. | Rotate Left                                                     | . 163 |

| Figure 52. | Rotate Left through Carry                                       | . 165 |

| Figure 53. | Rotate Right                                                    | . 167 |

| Figure 54. | Rotate Right through Carry                                      | . 169 |

| Figure 55. | Shift Right                                                     | . 176 |

| Figure 56. | Swap Nibbles                                                    | . 182 |

| Figure 57. | Sample Program Structure                                        | . 187 |

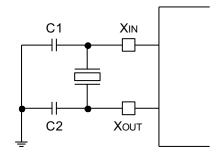

| Figure 58. | Main Oscillator Circuit                                         | . 190 |

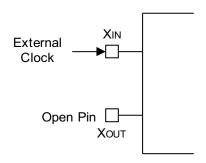

| Figure 59. | External Clock Circuit                                          | . 191 |

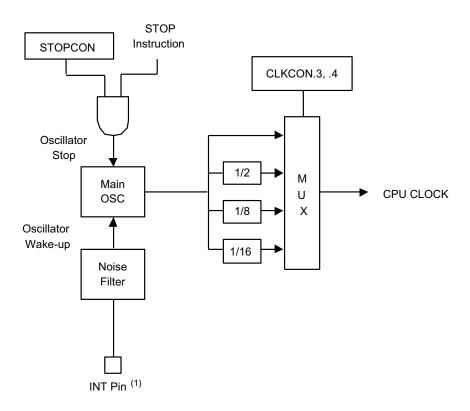

| Figure 60. | System Clock Circuit Diagram                                    | . 192 |

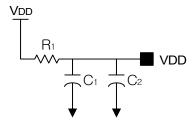

| Figure 61. | Power Circuit                                                   | . 193 |

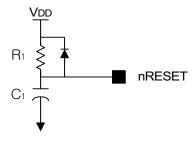

| Figure 62. | nRESET Circuit                                                  | . 194 |

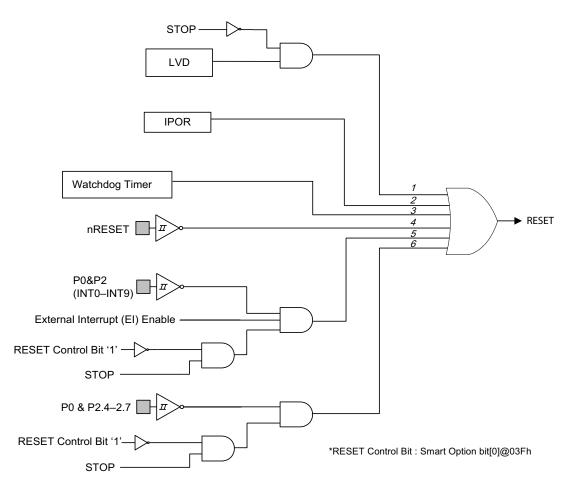

| Figure 63. | Reset Sources of the S3F80PB MCU                                | . 196 |

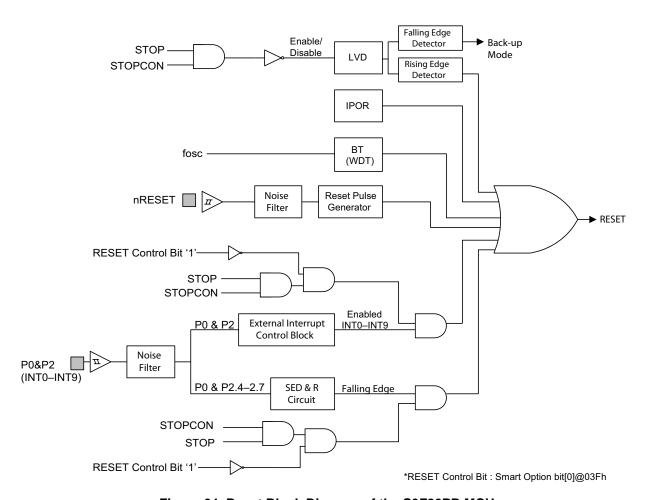

| Figure 64. | Reset Block Diagram of the S3F80PB MCU                          | . 197 |

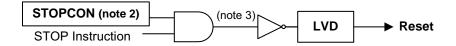

| Figure 65. | Reset Block Diagram by LVD for the S3F80PB MCU in Stop Mode     | . 198 |

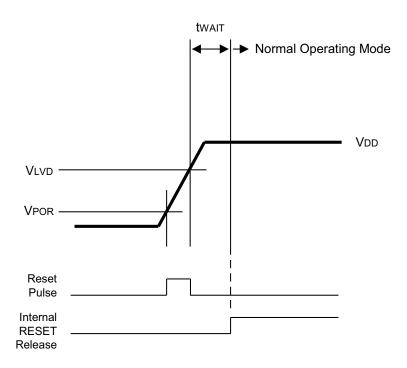

| Figure 66. | Timing Diagram for Internal Power-On Reset Circuit              | . 199 |

| Figure 67. | Reset Timing Diagram for the S3F80PB MCU in Stop Mode by IPOR . | . 200 |

| Figure 68. | Block Diagram for Backup Mode                                   | . 203 |

| Figure 69. | Timing Diagram for Backup Mode Input and Released by LVD        | . 204 |

| Figure 70. | Timing Diagram for Backup Mode Input in Stop Mode               | . 205 |

| Figure 71. | S3F80PB I/O Port Data Register Format                           | . 219 |

| Figure 72.  | Basic Timer and Timer 0 Block Diagram                    | . 244 |

|-------------|----------------------------------------------------------|-------|

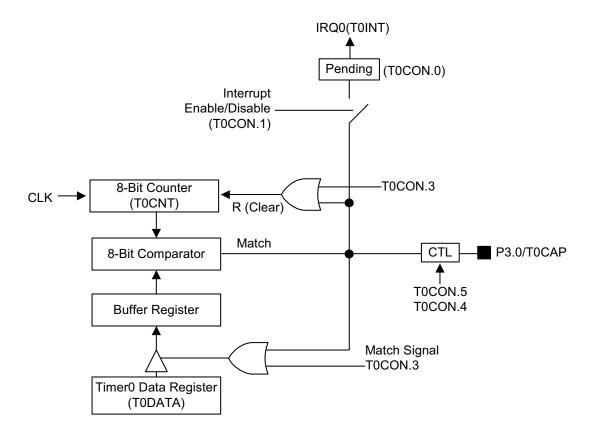

| Figure 73.  | Simplified Timer 0 Function Diagram: Interval Timer Mode | . 251 |

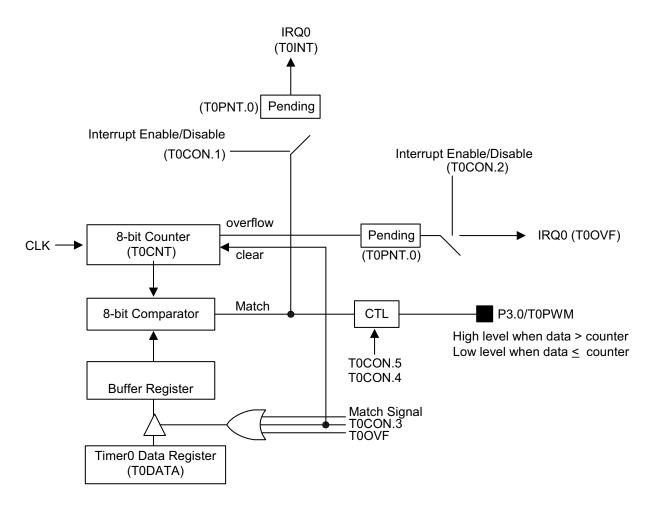

| Figure 74.  | Simplified Timer 0 Function Diagram: PWM Mode            | . 252 |

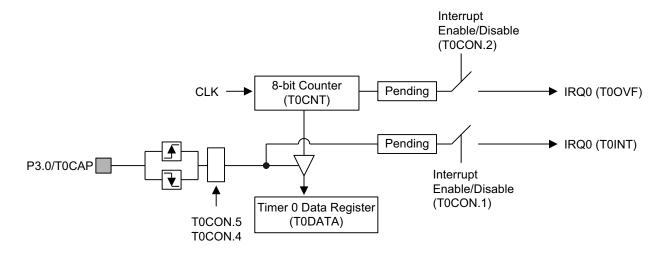

| Figure 75.  | Simplified Timer 0 Function Diagram: Capture Mode        | . 253 |

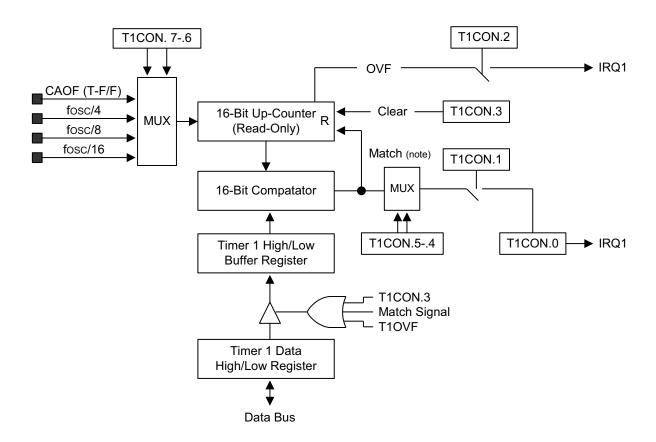

| Figure 76.  | Timer 1 Block Diagram                                    | . 256 |

| Figure 77.  | Simplified Timer 1 Function Diagram: Capture Mode        | . 261 |

| Figure 78.  | Simplified Timer 1 Function Diagram: Interval Timer Mode | . 262 |

| Figure 79.  | Counter A Block Diagram                                  | . 263 |

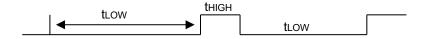

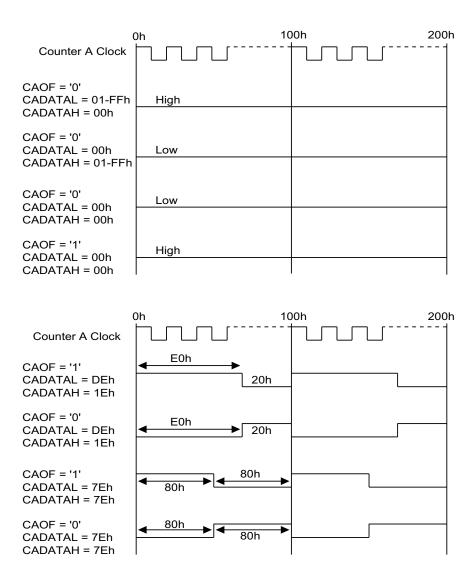

| Figure 80.  | Counter A Pulse Width                                    | . 266 |

| Figure 81.  | Counter A Output Flip-Flop Waveforms in Repeat Mode      | . 267 |

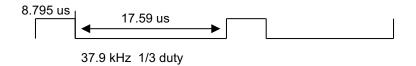

| Figure 82.  | 38 kHz, 1/3 Duty Carrier Frequency                       | . 267 |

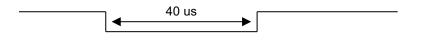

| Figure 83.  | One-Shot Mode                                            | . 268 |

| Figure 84.  | Timer 2 Block Diagram                                    | . 270 |

| Figure 85.  | Simplified Timer 2 Function Diagram: Capture Mode        | . 275 |

| Figure 86.  | Simplified Timer 2 Function Diagram: Interval Timer Mode | . 276 |

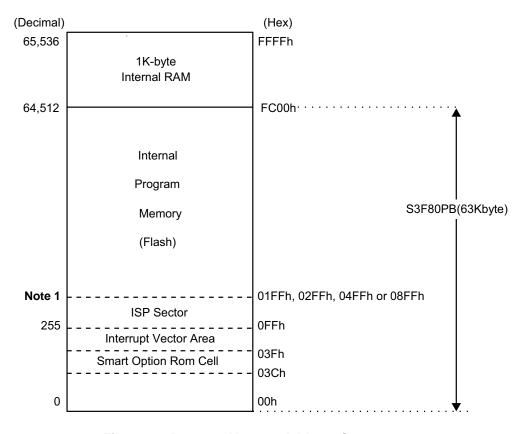

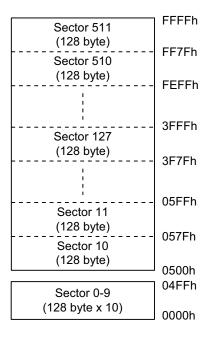

| Figure 87.  | Program Memory Address Space                             | . 279 |

| Figure 88.  | Sector Configurations in User Program Mode               | 284   |

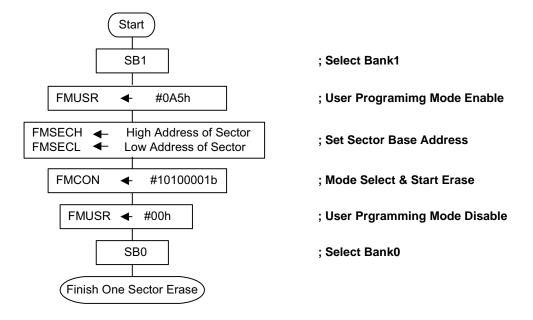

| Figure 89.  | Sector Erase Routine in User Program Mode                | . 285 |

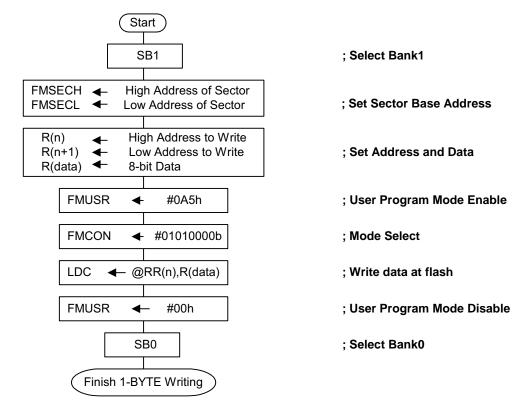

| Figure 90.  | Byte Program Flowchart in User Program Mode              | . 288 |

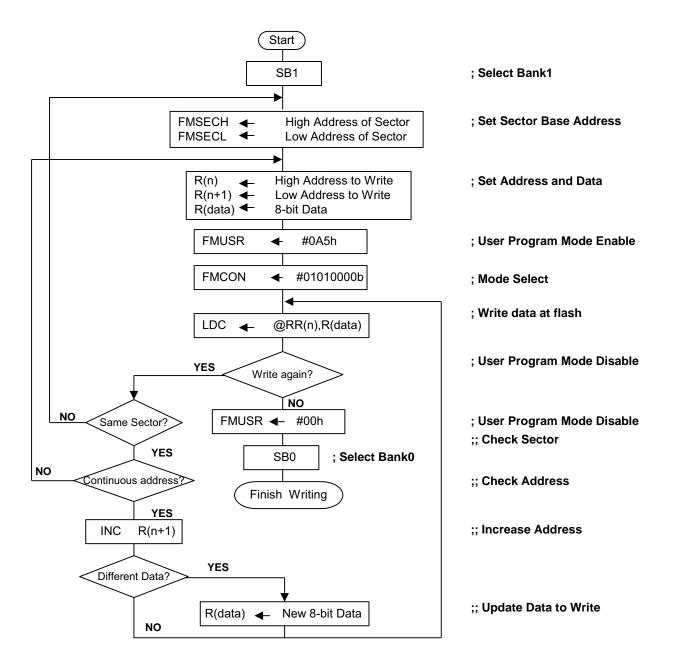

| Figure 91.  | Program Flowchart in User Program Mode                   | 289   |

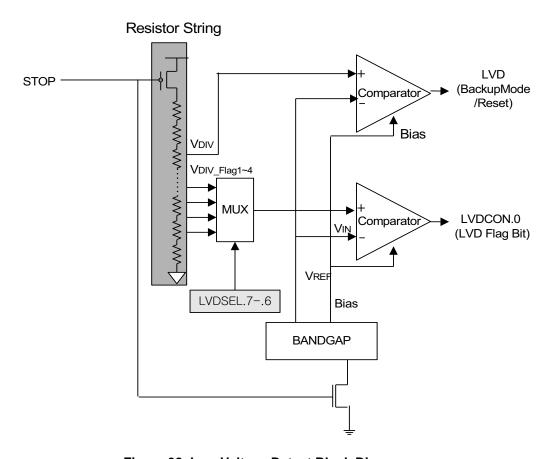

| Figure 92.  | Low Voltage Detect Block Diagram                         | . 295 |

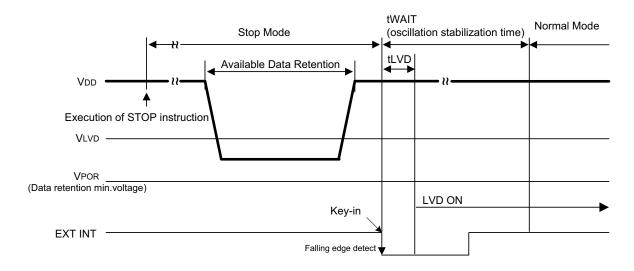

| Figure 93.  | Stop Mode to Normal Mode Timing Diagram, #1 of 2         | . 303 |

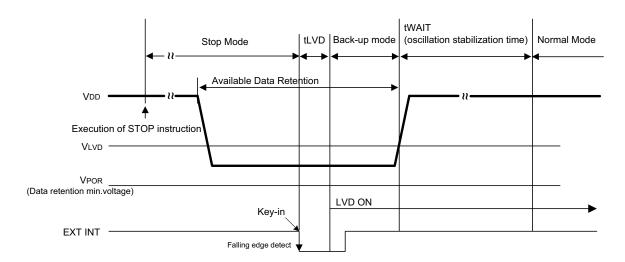

| Figure 94.  | Stop Mode to Normal Mode Timing Diagram, #2 of 2         | . 304 |

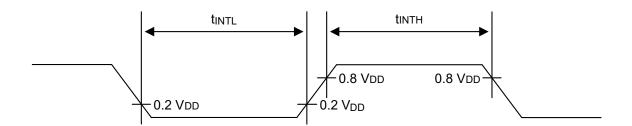

| Figure 95.  | Input Timing for External Interrupts, Ports 0 and 2      | . 304 |

| Figure 96.  | Input Timing for Reset (nRESET Pin)                      | . 305 |

| Figure 97.  | Operating Voltage Range                                  | . 307 |

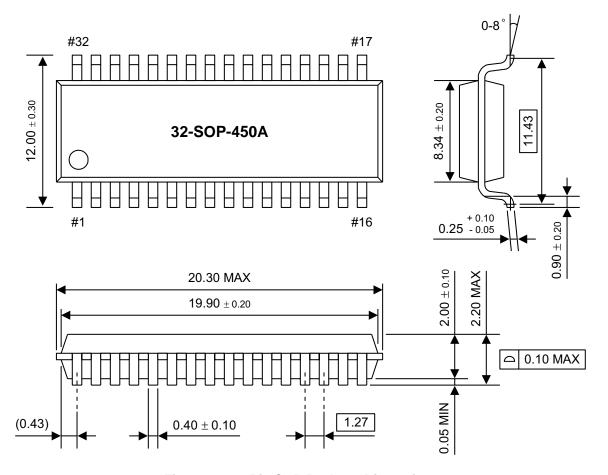

| Figure 98.  | 32-Pin SOP Package Dimension                             | . 309 |

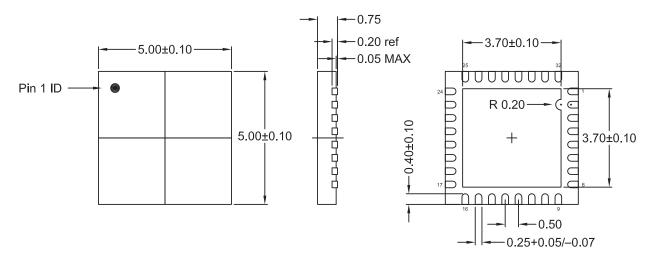

| Figure 99.  | 32-Pin ELP Package Dimension                             | 310   |

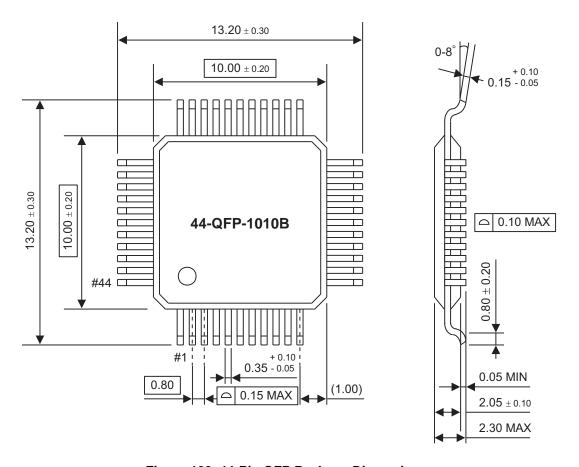

| Figure 100. | 44-Pin QFP Package Dimension                             | . 311 |

| Figure 101. | 44-Pin ELP Package Dimension                             | 312   |

| Figure 102. | Development System Configuration                         | . 315 |

| Figure 103. | TB80P0 Target Board Configuration                        | . 316 |

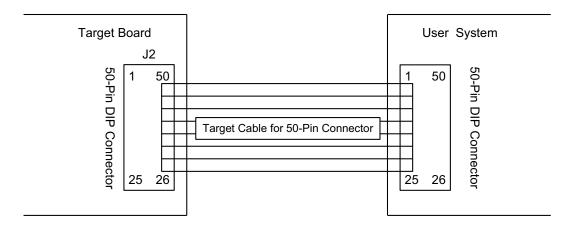

| Figure 104. | 50-Pin Connector Pin Assignment, User System             | . 319 |

| Figure 105. | TB80PB Probe Adapter Cable                               | . 320 |

|             |                                                          |       |

# List of Tables

| Table 1.  | Pin Descriptions, 32-Pin SOP/ELP Packages            | 8    |

|-----------|------------------------------------------------------|------|

| Table 2.  | Pin Descriptions, 44-Pin QFP/ELP Packages            | . 11 |

| Table 3.  | S3F80PB Register Types                               | . 24 |

| Table 4.  | Register Page Pointer                                | . 26 |

| Table 5.  | Register Pointer 0                                   | . 39 |

| Table 6.  | Register Pointer 1                                   | . 39 |

| Table 7.  | Stack Pointer Low Byte                               | . 42 |

| Table 8.  | Set1, Bank0 Mapped Registers                         | . 57 |

| Table 9.  | Set1, Bank1 Mapped Registers                         | . 59 |

| Table 10. | External Memory Timing Register                      | . 60 |

| Table 11. | S3F80PB Interrupt Vectors                            | . 66 |

| Table 12. | Interrupt Control Register Overview                  | . 68 |

| Table 13. | Vectored Interrupt Source Control and Data Registers | . 70 |

| Table 14. | System Mode Register                                 | . 71 |

| Table 15. | Interrupt Mask Register                              | . 73 |

| Table 16. | Interrupt Priority Register                          | . 75 |

| Table 17. | Interrupt Request Register                           | . 76 |

| Table 18. | Instruction Pointer High Byte                        | . 80 |

| Table 19. | Instruction Pointer Low Byte                         | . 80 |

| Table 20. | Instruction Summary                                  | . 84 |

| Table 21. | System Flags Register                                | . 87 |

| Table 22. | Flags                                                | . 88 |

| Table 23. | Flag Notation Conventions                            | . 89 |

| Table 24. | Instruction Set Symbols                              | . 89 |

| Table 25. | Instruction Notation Conventions                     | . 90 |

| Table 26. | Op Code Quick Reference (0–7)                        | . 91 |

| Table 27. | Op Code Quick Reference (8–F)                        | . 92 |

| Table 28. | Condition Codes                                      | . 93 |

| Table 29. | DA Instruction                                       | 120  |

| Table 30. | System Clock Control Register                        | 193  |

| Table 31. | Falling and Rising Time of Operating Voltage         | 194  |

| Table 32. | Reset Conditions in Stop Mode                        | 201  |

| Table 33. | Stop Control Register                                | 208  |

| Table 34. | Set 1, Bank 0 Register Values After Reset              | 210 |

|-----------|--------------------------------------------------------|-----|

| Table 35. | Set1, Bank1 Register Values After Reset                | 212 |

| Table 36. | Smart Option Reset Generation                          | 213 |

| Table 37. | Guideline for Unused Pins to Reduced Power Consumption | 214 |

| Table 38. | Summary of Each Mode                                   | 215 |

| Table 39. | Reset Source Indicating Register                       | 216 |

| Table 40. | State of RESETID Depends on Reset Source               | 216 |

| Table 41. | S3F80PB Port Configuration Overview (44-Pin QFP, ELP)  | 217 |

| Table 42. | S3F80PB Port Configuration Overview (32-Pin SOP, ELP)  | 218 |

| Table 43. | Port Data Register Summary                             | 219 |

| Table 44. | Port 0 Control                                         | 220 |

| Table 45. | Port 0 Control Low Byte Register                       | 221 |

| Table 46. | Port 0 External Interrupt Enable Register              | 222 |

| Table 47. | Port 0 External Interrupt Pending Register             | 223 |

| Table 48. | Port 0 Pull-Up Resistor Enable Register                | 224 |

| Table 49. | Port 1 Control High Byte Register                      | 226 |

| Table 50. | Port 1 Control Low Byte Register                       | 227 |

| Table 51. | Port 1 Output Pull-Up Resistor Enable Register         | 228 |

| Table 52. | Port 2 Control High Byte Register                      | 229 |

| Table 53. | Port 2 Control Low Byte Register                       | 230 |

| Table 54. | Port 2 External Interrupt Enable Register              | 231 |

| Table 55. | Port 2 Output Mode Selection Register                  | 232 |

| Table 56. | Port 2 External Interrupt Pending Register             | 233 |

| Table 57. | Port 2 Pull-Up Resistor Enable Register                | 234 |

| Table 58. | Port 3 Control Register                                | 236 |

| Table 59. | Function Description and Pin Assignment of P3CON       | 237 |

| Table 60. | Port 3 Output Pull-Up Resistor Enable Register         | 238 |

| Table 61. | Port 3[4:5] Control Register                           | 239 |

| Table 62. | Port 4 Control Register                                | 240 |

| Table 63. | Port 4 Control High Byte Register                      | 241 |

| Table 64. | Port 4 Control Low Byte Register                       | 242 |

| Table 65. | Port 4 Output Pull-Up Resistor Enable Register         | 243 |

| Table 66. | Basic Timer Control Register                           | 247 |

| Table 67. | Timer 0 Control Register                               | 249 |

| Table 68. | Timer 0 Reference Data Register                        | 250 |

| Table 69. | Timer 1 Control Register                               | 258 |

| Table 70.  | Timer 1 Counter High Byte Register                   | 259   |

|------------|------------------------------------------------------|-------|

| Table 71.  | Timer 1 Counter Low Byte Register                    | 259   |

| Table 72.  | Timer 1 Data High Byte Register                      | 259   |

| Table 73.  | Timer 1 Data Low Byte Register                       | 260   |

| Table 74.  | Counter A Control Register                           | 264   |

| Table 75.  | Counter A Data High Byte Register                    | 265   |

| Table 76.  | Counter A Data Low Byte Register                     | 265   |

| Table 77.  | Timer 2 Control Register                             | . 272 |

| Table 78.  | Timer 2 Counter High Byte Register                   | 273   |

| Table 79.  | Timer 2 Counter Low Byte Register                    | 273   |

| Table 80.  | Timer 2 Data High Byte Register                      | 273   |

| Table 81.  | Timer 2 Data Low Byte Register                       | 274   |

| Table 82.  | Reset Vector Address                                 | 280   |

| Table 83.  | ISP Sector Size                                      | 280   |

| Table 84.  | Flash Memory Control Register                        | 281   |

| Table 85.  | Flash Memory User Programming Enable Register        | 282   |

| Table 86.  | Flash Memory Sector Address High Byte Register       | . 283 |

| Table 87.  | Flash Memory Sector Address Low Byte Register        | 283   |

| Table 88.  | LVD Voltage Gap Characteristics                      | 296   |

| Table 89.  | LVD Flag Gap Characteristics                         | . 297 |

| Table 90.  | LVD Enable Time                                      | . 297 |

| Table 91.  | LVD Control Register                                 | . 297 |

| Table 92.  | LVD Flag Level Selection Register                    | . 298 |

| Table 93.  | Absolute Maximum Ratings                             | 300   |

| Table 94.  | DC Electrical Characteristics                        | 300   |

| Table 95.  | LVD Adder Current in Backup Mode                     | 301   |

| Table 96.  | Low Voltage Detect Circuit                           | 302   |

| Table 97.  | Low Voltage Detect Circuit                           | 302   |

| Table 98.  | LVD Enable Time                                      | 302   |

| Table 99.  | Power On Reset Circuit                               | 303   |

| Table 100. | Data Retention Supply Voltage in Stop Mode           | 303   |

| Table 101. | AC Electrical Characteristics                        | 304   |

| Table 102. | Oscillation Characteristics                          | 305   |

| Table 103. | Input/Output Capacitance                             | 306   |

| Table 104. | Oscillation Stabilization Time                       | 306   |

| Table 105. | AC Electrical Characteristics for Internal Flash ROM | 307   |

| Table 106. | ESD Characteristics                      | 308 |

|------------|------------------------------------------|-----|

| Table 107. | Flash Operations in Tool Program Mode    | 313 |

| Table 108. | Operating Mode Selection Criteria        | 314 |

| Table 109. | TB80PB Jumper Settings                   | 317 |

| Table 110. | TB80PB Target Board LEDs                 | 318 |

| Table 111. | Ordering Information for the S3F80PB MCU | 321 |

## Chapter 1. Overview

Zilog's S3 Family of 8-bit single-chip microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and multiple Flash memory sizes. Important CPU features include:

- Efficient register-oriented architecture

- Selectable CPU clock sources

- Idle and Stop power-down mode release by interrupts

- Built-in basic timer with watchdog function

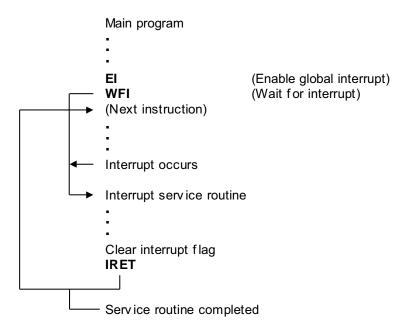

A sophisticated interrupt structure recognizes up to eight interrupt levels. Each level can include one or more interrupt sources and vectors. Fast interrupt processing (i.e., within a minimum four CPU clocks) can be assigned to specific interrupt levels.

### 1.1. S3F80PB Microcontroller

The S3F80PB MCU features 63KB of Flash ROM memory. Using a proven modular design approach, the S3F80PB MCU was developed by integrating the following peripheral modules with the SAM8 RC core:

- Internal LVD circuit and 16-bit programmable pins for external interrupts

- One 8-bit basic timer for oscillation stabilization and watchdog function (system reset)

- One 8-bit timer/counter with three operating modes

- Two 16-bit timer/counters with selectable operating modes

- One 8-bit counter with automatic reload function and one-shot or repeat control

The S3F80PB MCU is a versatile general-purpose microcontroller that is especially suitable for use as remote transmitter controller. It is currently available in 32-pin SOP, 32-pin ELP, 44-pin QFP, 44-pin ELP, and Pellet (Die) packages.

### 1.2. Features

The S3F80PB MCU offers the following features:

SAM8 RC CPU core

- Program memory:

- 63 KB internal Flash memory

- 10 years data retention

- Endurance: 10,000 erase/program cycles

- Byte-programmable

- User-programmable by LDC instruction

- Executable memory: 1KB RAM

- Data memory: 272-byte general-purpose RAM

- Instruction set:

- 78 instructions

- Idle and Stop instructions added for power-down modes

- Instruction execution time: 500ns at 8MHz f<sub>OSC</sub> (minimum)

- 24 interrupt sources with 18 vectors and 9 levels

- I/O ports:

- Four 8-bit I/O ports (P0-P2, P4) and one 6-bit I/O port (P3) for a total of 38-bit programmable pins (44-pin QFP)

- Three 8-bit I/O ports (P0-P2) and one 2-bit I/O port (P3) for a total of 26-bit programmable pins (32-pin SOP)

- Three 8-bit n-channel open-drain pins (P1, P2, and P4) and one 2-bit n-channel open-drain pin (P3; 44-pin QFP)

- Two 8-bit n-channel open-drain pins (P1, P2) and one 2-bit n-channel open-drain pin (P3; 32-pin SOP)

- Carrier frequency generator: one 8-bit counter with automatic reload function and oneshot or repeat control (Counter A)

- Basic timer and timer/counters:

- One programmable 8-bit basic timer (BT) for oscillation stabilization control or watchdog timer (software reset) function

- One 8-bit timer/counter (Timer 0) with three operating modes: Interval, Capture and PWM

- One 16-bit timer/counter (Timer 1) with two operating modes: Interval and Capture

- One 16-bit timer/counter (Timer 2) with two operating modes: Interval and Capture

- Backup Mode:

- When V<sub>DD</sub> is lower than V<sub>LVD</sub> and LVD is ON, the S3F80PB MCU enters Backup Mode to block oscillation

- When the reset pin is lower than the input low voltage  $(V_{IL})$ , the S3F80PB MCU enters Backup Mode to block oscillation and reduce current consumption

- Low Voltage Detect circuit:

- Low voltage detect to enter Backup Mode and Reset

- $1.65 \text{ V (typ.)} \pm 50 \text{ mV}.$

- Low voltage detect to control the LVD\_Flag bit at 1.90 V, 2.00 V, 2.10 V, and 2.20 V (typ.)  $\pm 100 \text{ mV}$  (selectable).

- LVD Reset enable:

- When voltage at  $V_{DD}$  is falling and passes  $V_{LVD}$ , the S3F80PB MCU enters Backup Mode

- When voltage at  $V_{DD}$  is rising, a reset pulse is generated at  $V_{DD} > V_{LVD}$

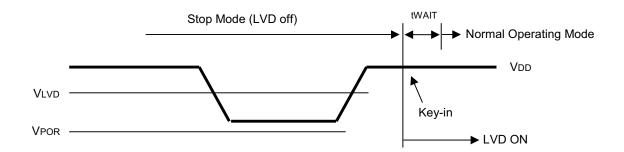

- LVD Stop Mode disable: if voltage at V<sub>DD</sub> does not fall to V<sub>POR</sub>, a reset pulse is not generated

- Operating temperature range: -25°C to +85°C

- Operating voltage range: 1.60V to 3.6V at 1 to 8MHz

- Packages:

- 32-pin SOP

- 32-pin ELP

- 44-pin QFP

- 44-pin ELP

An DXYS Company

## 1.3. Block Diagram

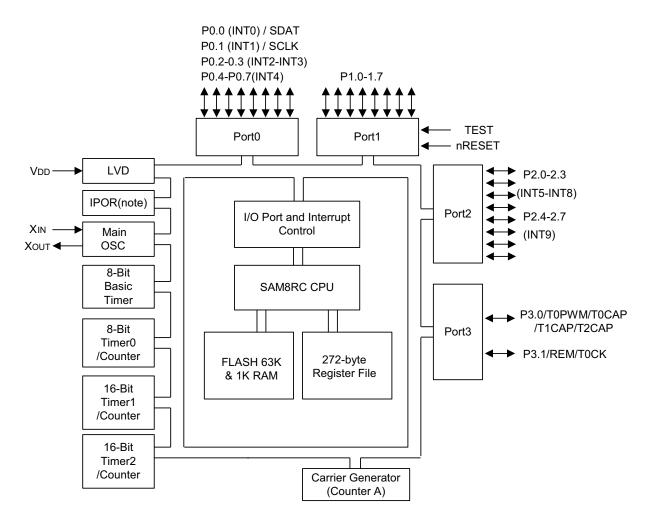

Figure 1shows a block diagram for the S3F80PB MCU's, 32-pin SOP and 32-pin ELP packages.

Figure 1. 32-Pin SOP/ELP Block Diagram

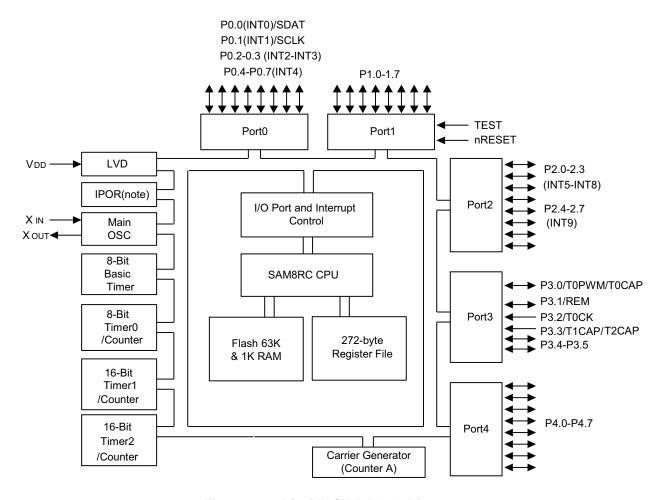

Figure 2shows a block diagram for the S3F80PB MCU's, 44-pin QFP and 44-pin ELP packages.

Figure 2. 44-Pin QFP/ELP Block Diagram

6

### 1.4. Pin Assignments

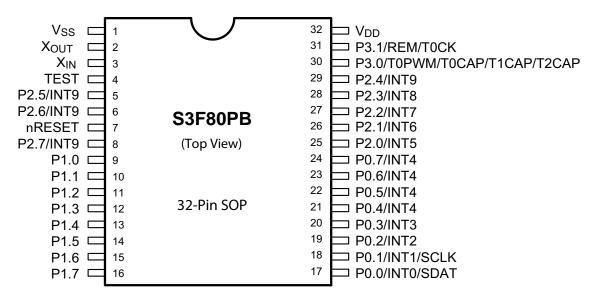

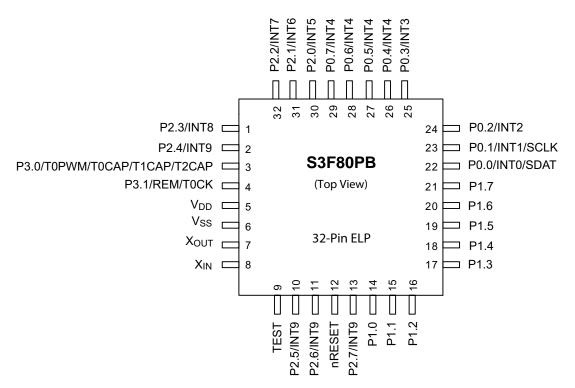

Figures 3 and 4 show the pin assignments for the 32-pin SOP and ELP packages, respectively.

Figure 3. Pin Assignments, 32-Pin SOP Package

Figure 4. Pin Assignments, 32-Pin ELP Package

Table 1 identifies each pin in the S3F80PB MCU's 32-pin SOP and 32-Pin ELP packages.

Table 1. Pin Descriptions, 32-Pin SOP/ELP Packages

| Pin Name  | Pin Description                                                                                                                                                                                                                                                                                                                                                           | Pin<br>Type | Circuit<br>Type | SOP<br>Pkg.<br>Pins | ELP<br>Pkg.<br>Pins            | Shared<br>Functions                                        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|---------------------|--------------------------------|------------------------------------------------------------|

| P0.0-P0.7 | I/O port with bit-programmable pins. Configurable to Input or Push-Pull Output Mode. Pull-up resistors can be assigned by software. Pins can be assigned individually as external interrupt inputs with noise filters, interrupt enable/disable, and interrupt pending control. In the tool mode, P0.0 and P0.1 are assigned as serial MTP interface pins; SDAT and SCLK. | I/O         | 1               | 17–24               | 22–29                          | External<br>Interrupts<br>INT0-INT3<br>INT4, SDAT,<br>SCLK |

| P1.0-P1.7 | I/O port with bit-programmable pins. Configurable to Input Mode or Output Mode. Pin circuits are either push-pull or n-channel open-drain type.                                                                                                                                                                                                                           | I/O         | 2               | 9–16                | 14–21                          | _                                                          |

| P2.0-P2.7 | I/O port with bit-programmable pins. Configurable to Input Mode, Push-Pull Output Mode, or n-channel Open-Drain Output Mode. Pull-up resistors can be assigned by software. Pins can be assigned individually as external interrupt inputs with noise filters, interrupt enable/disable, and interrupt pending control.                                                   | I/O         | 3               | 25–29,<br>5, 6, 8   | 30–32,<br>1–2,<br>10–11,<br>13 | External<br>Interrupts<br>INT5–INT8,<br>INT9               |

| P3.0      | I/O port with a bit-programmable pin. Configurable to Input Mode, Push-Pull Output Mode, or n-channel Open-Drain Output Mode. Input Mode with a pull-up resistor can be assigned by software. This Port 3 pin features high current drive capability. Also P3.0 can be assigned individually as an output pin for TOPWM or input pin for TOCAP/ T1CAP/T2CAP.              | I/O         | 4               | 30                  | 3                              | T0PWM/T0CAP/<br>T1CAP/T2CAP                                |

Table 1. Pin Descriptions, 32-Pin SOP/ELP Packages (Continued)

| Pin Name                           | Pin Description                                                                                                                                                                                                                                                                                                                              | Pin<br>Type | Circuit<br>Type | SOP<br>Pkg.<br>Pins | ELP<br>Pkg.<br>Pins | Shared<br>Functions |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|---------------------|---------------------|---------------------|

| P3.1                               | I/O port with a bit-programmable pin. Configurable to Input Mode, Push-Pull Output Mode, or n-channel Open-Drain Output Mode. Input Mode with a pull-up resistor can be assigned by software. This Port 3 pin features high current drive capability. Also P3.1 can be assigned individually as an output pin for REM or input pin for TOCK. | I/O         | 5               | 31                  | 4                   | REM/T0CK            |

| X <sub>OUT</sub> , X <sub>IN</sub> | System clock input and output pins                                                                                                                                                                                                                                                                                                           | _           | _               | 2, 3                | 7, 8                | _                   |

| nRESET                             | System reset signal input pin and Backup Mode input. Zilog recommends adding a 0.1 µF capacitor between nRESET pin and V <sub>SS</sub> for better noise immunity.                                                                                                                                                                            | I           | 7               | 7                   | 12                  | -                   |

| TEST                               | Test signal input pin. If on board programming is required, Zilog recommends to add a 0.1 µF capacitor between the TEST pin and V <sub>SS</sub> for better noise immunity; otherwise, connect the TEST pin to V <sub>SS</sub> directly.                                                                                                      | I           | -               | 4                   | 9                   | -                   |

| $V_{DD}$                           | Power supply input pin                                                                                                                                                                                                                                                                                                                       | _           | _               | 32                  | 5                   | -                   |

| $V_{SS}$                           | Ground Pin                                                                                                                                                                                                                                                                                                                                   | -           | -               | 1                   | 6                   | -                   |

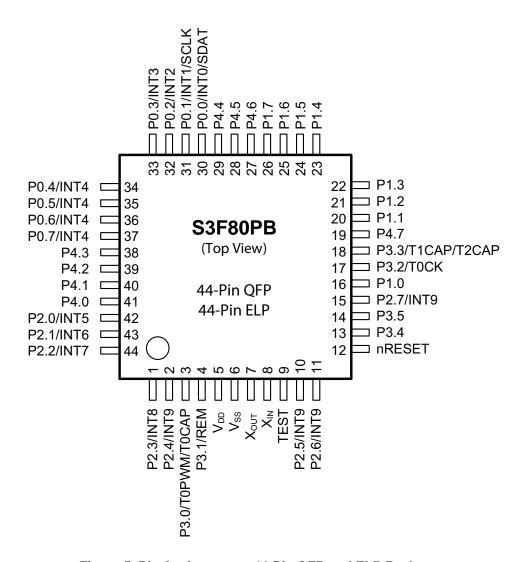

Figure 5 shows the pin assignments for both the 44-pin QFP and 44-pin ELP packages.

Figure 5. Pin Assignments, 44-Pin QFP and ELP Packages

Table 2 identifies each pin in the S3F80PB MCU's 44-pin QFP and 44-Pin ELP packages.

Table 2. Pin Descriptions, 44-Pin QFP/ELP Packages

| Pin Name               | Pin Description                                                                                                                                                                                                                                                                                                                                                       | Pin<br>Type | Circuit<br>Type | QFP<br>Pkg.<br>Pins | ELP<br>Pkg.<br>Pins              | Shared<br>Functions                                         |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|---------------------|----------------------------------|-------------------------------------------------------------|

| P0.0-P0.7              | I/O port with bit-programmable pins. Configurable to Input or Push-Pull Output Mode. Pull-up resistors can be assigned by software. Pins can be assigned individually as external interrupt inputs with noise filters, interrupt enable/disable, and interrupt pending control. In Tool Mode, P0.0 and P0.1 are assigned as serial MTP interface pins; SDAT and SCLK. | I/O         | 1               | 30–37               | 30–37                            | External<br>Interrupts<br>INT0-INT3,<br>INT4, SDAT,<br>SCLK |

| P1.0-P1.7              | I/O port with bit-programmable pins. Configurable to Input Mode or Output Mode. Pin circuits are either Push-Pull or n-Channel Open-Drain type.                                                                                                                                                                                                                       | I/O         | 2               | 16,<br>20–26        | 16,<br>20–26                     | _                                                           |

| P2.0–P2.3<br>P2.4–P2.7 | I/O port with bit-programmable pins. Configurable to Input Mode, Push-Pull Output Mode, or n-Channel Open-Drain Output Mode. Pull-up resistors can be assigned by software. Pins can be assigned individually as external interrupt inputs with noise filters, interrupt enable/disable, and interrupt pending control.                                               | I/O         | 3               | 1, 2,               | 42–44,<br>1, 2,<br>10, 11,<br>15 | External<br>Interrupts<br>INT5–INT8,<br>INT9                |

| P3.0                   | I/O port with a bit-programmable pin. Configurable to Input Mode, Push-Pull Output Mode, or n-Channel Open-Drain Output Mode. Input Mode with a pull-up resistor can be assigned by software. This Port 3 pin features high current drive capability. Also P3.0 can be assigned individually as an output pin for TOPWM or input pin for TOCAP.                       | I/O         | 4               | 3                   | 3                                | T0PWM/T0CAP                                                 |

Table 2. Pin Descriptions, 44-Pin QFP/ELP Packages (Continued)

| Pin Name                           | Pin Description                                                                                                                                                                                                                                                                                                        | Pin<br>Type | Circuit<br>Type | QFP<br>Pkg.<br>Pins | ELP<br>Pkg.<br>Pins    | Shared<br>Functions |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|---------------------|------------------------|---------------------|

| P3.1                               | I/O port with a bit-programmable pin. Configurable to Input Mode, Push-Pull Output Mode, or n-Channel Open-Drain Output Mode. Input Mode with a pull-up resistor can be assigned by software. This Port 3 pin features high current drive capability. Also P3.1 can be assigned individually as an output pin for REM. | I/O         | 5               | 4                   | 4                      | REM                 |

| P3.2–P3.3                          | C-MOS Input port with a pull-up resistor                                                                                                                                                                                                                                                                               | I           | 6               | 17, 18              | 17, 18                 | T0CK<br>T1CAP/T2CAP |

| P3.4-P3.5                          | I/O port with bit-programmable pins. Configurable to input mode or output mode. Pin circuits are either push-pull or n-channel open-drain type. Pull-up resistors can be assigned by software.                                                                                                                         | I/O         | 2               | 13, 14              | 13, 14                 | -                   |

| P4.0-P4.7                          | I/O port with bit-programmable pins. Configurable to input mode or output mode. Pin circuits are either push-pull or n-channel open-drain type.                                                                                                                                                                        | I/O         | 2               |                     | 38–41,<br>27–29,<br>19 | -                   |

| X <sub>OUT</sub> , X <sub>IN</sub> | System clock input and output pins                                                                                                                                                                                                                                                                                     | -           | _               | 7, 8                | 7, 8                   | _                   |

| nRESET                             | System reset signal input pin and Backup Mode input. Zilog recommends adding a 0.1 µF capacitor between nRESET pin and V <sub>SS</sub> for better noise immunity.                                                                                                                                                      | I           | 7               | 12                  | 12                     | -                   |

| TEST                               | Test signal input pin. If on board programming is required, Zilog recommends adding a 0.1 µF capacitor between the TEST pin and V <sub>SS</sub> for better noise immunity; otherwise, connect the TEST pin to V <sub>SS</sub> directly.                                                                                | I           | _               | 9                   | 9                      | -                   |

| $V_{DD}$                           | Power supply input pin                                                                                                                                                                                                                                                                                                 | -           | -               | 5                   | 5                      | _                   |

| $V_{SS}$                           | Ground Pin                                                                                                                                                                                                                                                                                                             | _           | _               | 6                   | 6                      | _                   |

### 1.5. Pin Circuits

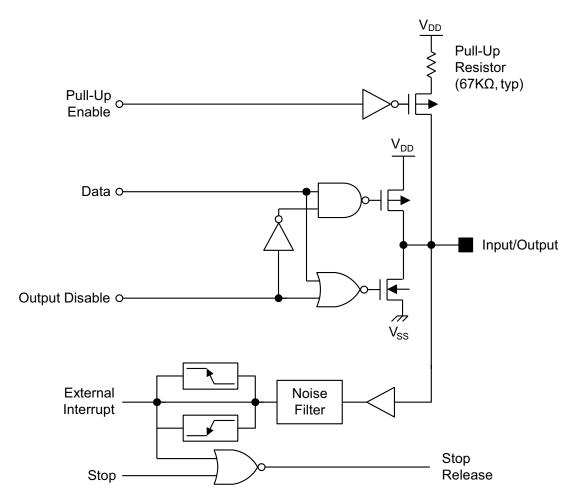

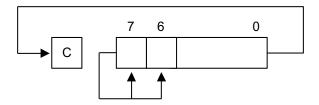

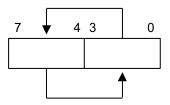

Figure 6 shows the Type 1 pin circuit for Port 0.

Figure 6. Port 0 Pin Circuit, Type 1

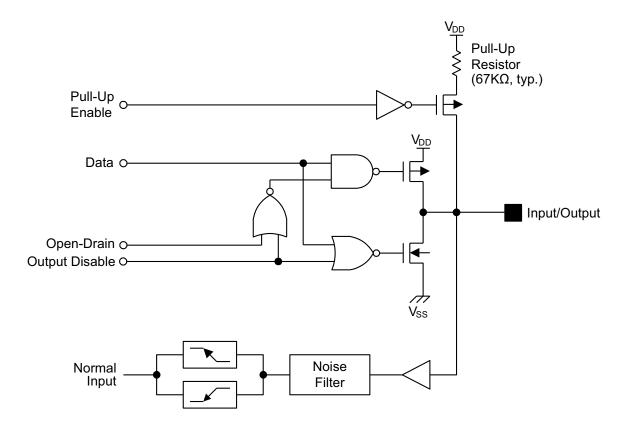

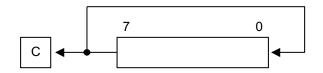

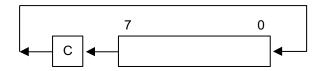

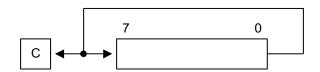

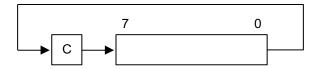

Figure 7 shows the Type 2 pin circuit for Port 1, Port 4, P3.4, and P3.5.

Figure 7. Port 1, Port 4, P3.4 and P3.5 Pin Circuit, Type 2

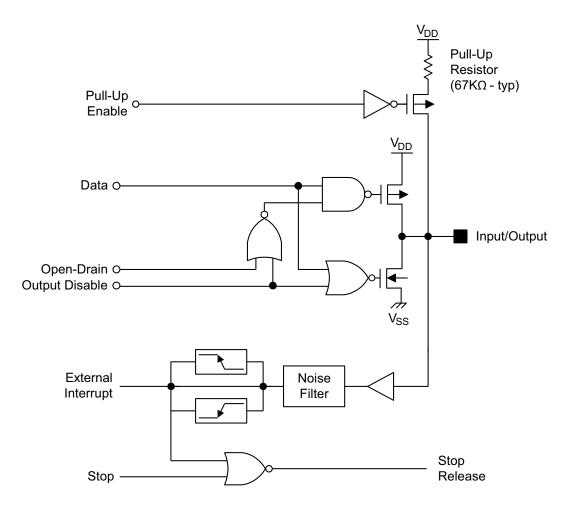

Figure 8 illustrates the Type 3 pin circuit for Port 2.

Figure 8. Port 2 Pin Circuit, Type 3

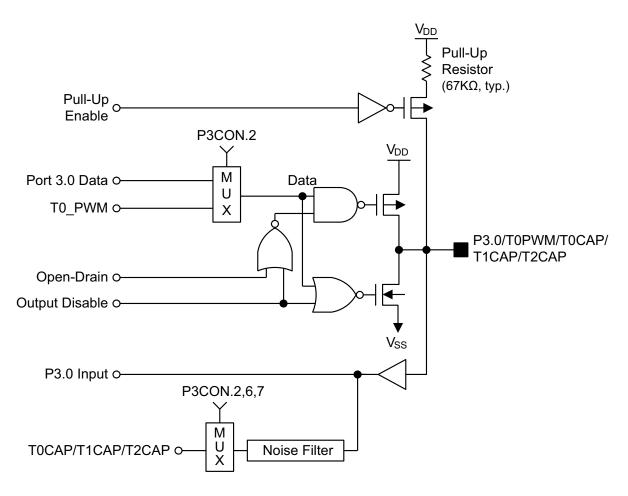

Figure 9 shows the Type 4 pin circuit for Port 3.0.

Figure 9. Port 3.0 Pin Circuit, Type 4

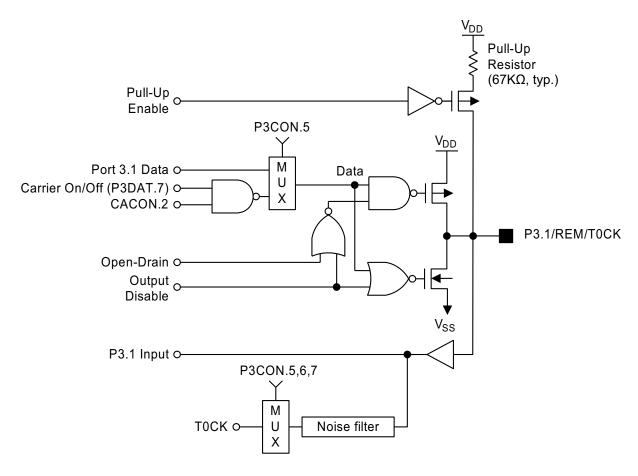

Figure 10 shows the Type 5 pin circuit for P3.1.

Figure 10. P3.1 Pin Circuit, Type 5

18

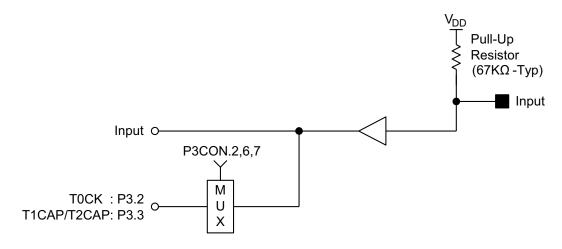

Figure 11 shows the Type 6 pin circuit for P3.2 and P3.3.

Figure 11. P3.2 and P3.3 Pin Circuit, Type 6

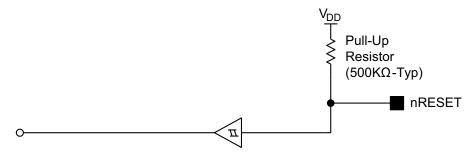

Figure 12 shows the Type 7 pin circuit for nRESET.

Figure 12. nRESET Pin Circuit, Type 7

## Chapter 2. Address Space

The S3F80PB microcontroller features two types of address spaces:

- Internal program (Flash) memory

- Internal register file

A 16-bit address bus supports program memory operations. A separate 8-bit register bus carries addresses and data between the CPU and the register file.

The S3F80PB MCU features 63 KB of programmable internal Flash ROM. An external memory interface is not implemented.

The internal register file contains 333 mapped registers; of these, 272 bytes are designated for general-purpose use. This number includes a 16-byte working register common area that is used as a scratch area for data operations, a 192-byte prime register area, and a 64-byte area, Set2, that is also used for stack operations. Twenty-two 8-bit registers are used for CPU and system control; 39 registers are mapped peripheral control and data registers.

### 2.1. Program Memory

Program memory stores program code or table data. The S3F80PB MCU includes a memory map option which is 63KB of internal programmable Flash memory and 2KB of executable RAM.

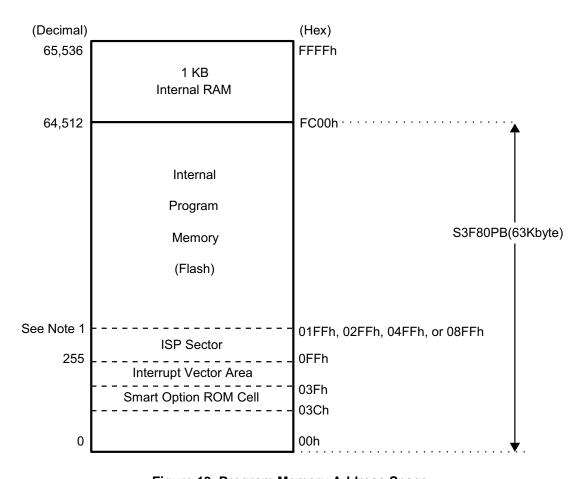

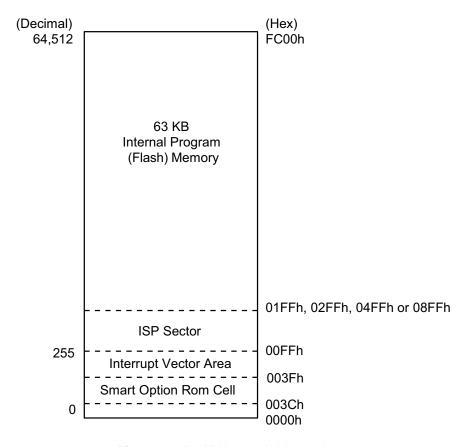

The program memory address range is therefore 0000h-FFFFh of Flash memory, as shown in Figure 13.

Figure 13. Program Memory Address Space

- Notes: 1. In Figure 13, the size of the ISP sector can be varied by the Smart Option. According to the Smart Option settings, the ISP reset vector address can be changed to one of the following addresses: 200h, 300h, 500h, or 900h.

- 2. The ISP sector can store on-board program software. To learn more, see the Embedded Flash Memory Interface chapter on page 277.

The first 256 bytes of the program memory (0h-0FFh) are reserved for interrupt vector addresses. Unused locations (in the 0000h-00FFh address range, with the exception of 03Ch, 03Dh, 03Eh, and 03Fh) can be used as normal program memory. The 03Ch, 03Dh, 03Eh, and 03Fh locations are used as a Smart Option ROM cell. Avoid overwriting vector addresses stored in these locations when using the vector address area to store program code.

By default, the program memory address at which program execution starts after reset is 0100h. The reset vector address can be changed by setting the Smart Option when using ISP sectors for ISP software storage; see Figure 14 and the Smart Option section, which follow.

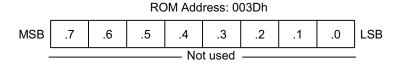

# 2.1.1. Smart Option

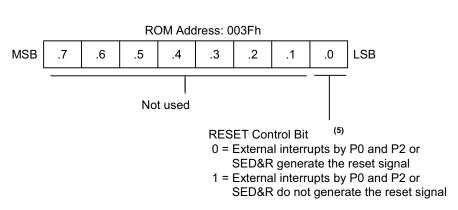

The *Smart Option*, diagrammed in Figure 14, is the program memory option for setting the starting condition of the S3F80PB MCU. The program memory addresses used by the Smart Option are from 003Ch to 003Fh. The S3F80PB MCU uses only addresses in the range 003Eh to 003Fh.

Users can write any value to the unused addresses (003Ch and 003Dh). The default value of the Smart Option bits in program memory is 0FFh; the normal reset vector address, 100h, is ISP protection-disabled. Before executing program memory code, set the Smart Option bits according to the preferred hardware option.

Figure 14. Smart Option

- **Notes:** 1. In Figure 14, by setting ISP reset vector change selection bit (3Eh. 7) to 0, the ISP area becomes available. If this bit is 1, 3Eh. 6 and 3Eh. 5 are rendered meaningless.

- 2. If the ISP reset vector change selection bit (3Eh. 7) is 0, the user must change the ISP reset vector address from 0100h to an address at which the user prefers to set a reset (i.e., 0200h, 0300h, 0500h, or 0900h). If the reset vector address is 0200h, the ISP area can be assigned from 0100h to 01FFh (an area of 256 bytes). If 0300h, the ISP area can be assigned from 0100h to 02FFh (512 bytes). If 0500h, the ISP area can be assigned from 0100h to 04FFh (1024 bytes). If 0900h, the ISP area can be assigned from 0100h to 08FFh (2048 bytes).

- 3. If the ISP protection enable/disable bit is 0, the ISP area selected by 3Eh. 1 and 3Eh. 0 cannot be erased or programmed in Flash memory.

- 4. A suitable ISP protection size can be selected using 3Eh.1 and 3Eh.0. If the ISP protection enable/disable bit (3Eh. 2) is 1, 3Eh. 1 and 3Eh. 0 are rendered meaningless.

- 5. External interrupts can be used to release Stop Mode. When the RESET control bit (3Fh.0) is 0 and external interrupts are enabled, these external interrupts wake the MCU from Stop Mode and generate a reset signal. Any falling edge input signals of P0 or P2.4–P2.7 can wake the MCU from Stop Mode and generate this reset signal. When the RESET control bit (3Fh.0) is 1, the S3F80PB MCU only releases Stop Mode and does not generate a reset signal.

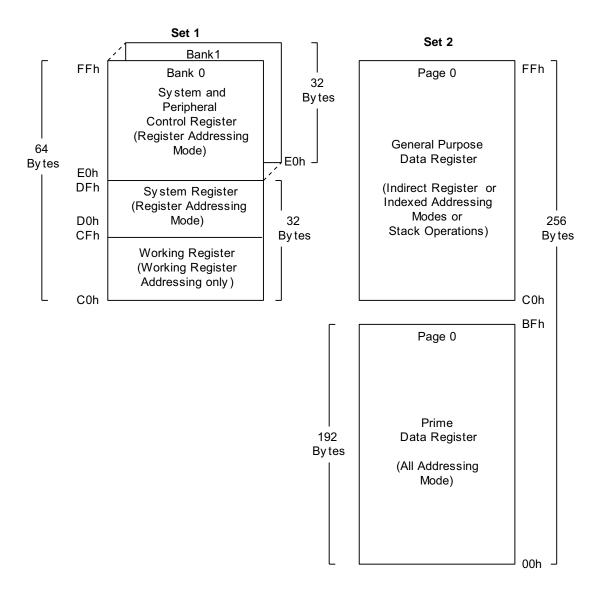

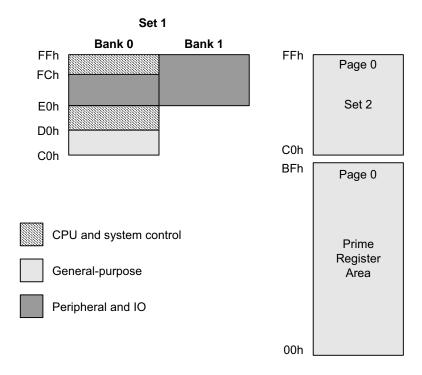

# 2.2. Register Architecture

In the S3F80PB implementation, the upper 64-byte area of register files is expanded to two 64-byte areas, called *Set1* and *Set2*. The upper 32-byte area of Set1 is further expanded into two 32-byte register banks (i.e., Bank0 and Bank1). The lower 32-byte area is a single 32-byte common area.

In the S3F80PB MCU, the total number of addressable 8-bit registers is 333. Of these 333 registers, 22 bytes are designated for the CPU and system control registers, 39 bytes are designated for the peripheral control and data registers, 16 bytes are used as shared working registers, and 272 registers are designated for general-purpose use.

The extension of the register space into separately-addressable areas (i.e., sets and banks) is supported by multiple addressing mode restrictions: the select bank instructions, SB0 and SB1.

Specific register types and the area occupied in the S3F80PB internal register space are summarized in Table 3.

#### Table 3. S3F80PB Register Types

| Register Type                                                                                                                                    | Number of<br>Bytes |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| General-purpose registers, including the 16-byte common working register area, the 64-byte Set2 area and 192-byte prime register area of Page 0. | 272                |

| CPU and system control registers                                                                                                                 | 22                 |

| Mapped clock, peripheral, and I/O control and data registers (Bank0: 27 registers, Bank1: 12 registers)                                          | 39                 |

| Total addressable bytes                                                                                                                          | 333                |

Figure 15 shows the organization of the Internal Register File.

Figure 15. Internal Register File Organization

# 2.2.1. Register Page Pointer

The S3 Family architecture supports the logical expansion of the physical 333-byte internal register files (using an 8-bit data bus) into as many as 16 separately addressable register pages. Page addressing is controlled by the Register Page Pointer (PP; Set1, Bank0,

DFh). In the S3F80PB microcontroller, a paged register file expansion is not implemented, and the register page pointer settings therefore always point to Page 0.

Following a reset, the page pointer's source value (i.e., lower nibble) and destination value (i.e., upper nibble) are always 0000, automatically. Therefore, the S3F80PB MCU always selects Page 0 as the source and destination page for register addressing. These Page Pointer (PP) Register settings, as shown in Table 4, should not be modified during normal operation.

Table 4. Register Page Pointer (PP; Set1, Bank0)

| Bit   |                           | 7        | 6                           | 5 | 4           | 3   | 2 | 1 | 0 |

|-------|---------------------------|----------|-----------------------------|---|-------------|-----|---|---|---|

| Rese  | t                         | 0        | 0                           | 0 | 0           | 0   | 0 | 0 | 0 |

| R/W   |                           |          |                             |   | R/          | W   |   |   |   |

| Addr  | ess                       |          |                             |   | DI          | -Fh |   |   |   |

| Note: | R/W = read/wi             | ite.     |                             |   |             |     |   |   |   |

| Bit   | De                        | scriptio | on                          |   |             |     |   |   |   |

| [7:4] |                           |          | on Register<br>tination: Pa | _ | ection Bits |     |   |   |   |

| [3:0] |                           |          | egister Pag<br>rce: Page 0  |   | n Bits      |     |   |   |   |

| Note: | In the S3F80P shown above |          |                             |   |             |     |   |   |   |

# 2.2.2. Register Set1

The term *Set1* refers to the upper 64 bytes of the register file, locations C0h–FFh.

The upper 32-byte area of this 64-byte space (E0h–FFh) is divided into two 32-byte register banks, Bank0 and Bank1. The Set Register's SB0 or SB1 bank instructions are used to address one bank or the other. In the S3F80PB microcontroller, Bank1 is implemented. A hardware reset operation always selects Bank0 addressing.

The upper two 32-byte area of Set1, Bank0, (E0h-FFh) contain 31 mapped system and peripheral control registers. Additionally, the upper 32-byte area of Set1, Bank1 (E0h-FFh) contains 16 mapped peripheral control registers. The lower 32-byte area contains 15 system registers (D0h-DFh) and a 16-byte common working register area (C0h-CFh). Use the common working register area as a scratch area for data operations being performed in other areas of the register file.

Registers in the Set1 location are directly accessible at all times using the Register Addressing Mode. The 16-byte working register area can only be accessed using working register addressing. To learn more about working register addressing, see the <a href="Modes chapter">Addressing</a>. See the <a href="Modes chapter">Addressing</a> and times using the Register Addressing working register addressing, see the <a href="Modes chapter">Addressing</a> and <a href="Modes chapter">Modes</a> chapter on page 36.

# 2.2.3. Register Set2

The same 64-byte physical space that is used for Set1 location C0h–FFh is logically duplicated to add another 64 bytes of register space. This expanded area of the register file is called *Set2*. The Set2 locations (C0h–FFh) are accessible on Page 0 in the S3F80PB MCU's register space.

The logical division of Set1 and Set2 is maintained by means of addressing mode restrictions: Use only Register Addressing Mode to access Set1 locations; to access registers in Set2, you must use Register Indirect Addressing Mode or Indexed Addressing Mode. The Set2 register area is commonly used for stack operations.

# 2.2.4. Prime Register Space

The lower 192 bytes of the 256-byte physical internal register file (00h–BFh) are called the *prime register space* or, more simply, the *prime area*. Access the registers in this address using any addressing mode. (In other words, there is no addressing mode restriction for these registers, as is the case for Set1 and Set2 registers.) The prime register area on Page 0 is immediately addressable following a reset.

Figure 16 shows a map of the Set1, Set2, and prime register space.

Figure 16. Set1, Set2, and Prime Area Register Map

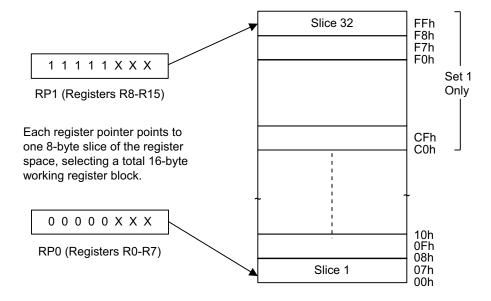

# 2.2.5. Working Registers

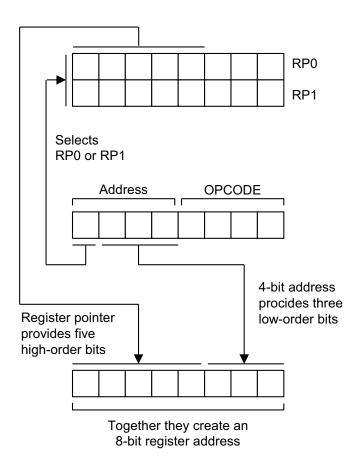

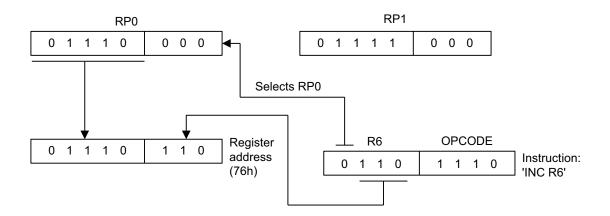

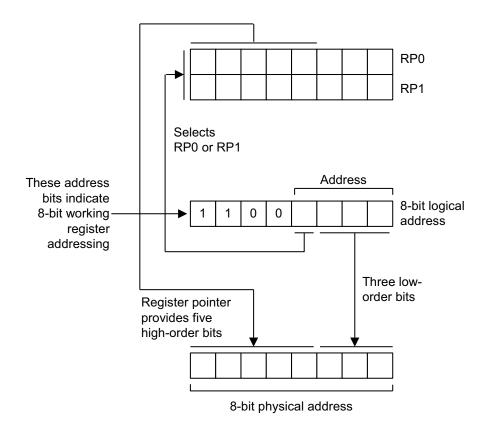

Instructions can access specific 8-bit registers or 16-bit register pairs using either 4-bit or 8-bit address fields. When the 4-bit working register addressing is used, the 256-byte register file can be seen by the programmer as consisting of thirty-two 8-byte register groups or slices. Each slice consists of eight 8-bit registers.

Using the two 8-bit register pointers, RP1 and RP0, two working register slices can be selected at any one time to form a 16-byte working register block. Using the register pointers, move this 16-byte register block anywhere in the addressable register file, except for the Set2 area.

The terms *slice* and *block* are used in this manual to help you visualize the size and relative locations of selected working register spaces:

- One working register slice is 8 bytes (eight 8-bit working registers; R0–R7 or R8–R15)

- One working register block is 16 bytes (sixteen 8-bit working registers; R0–R15)

All of the registers in an 8-byte working register slice feature the same binary value for their five most significant address bits, thereby making it possible for each register pointer to point to one of the 24 slices in the register file. The base addresses for the two selected 8-byte register slices are contained in register pointers RP0 and RP1.

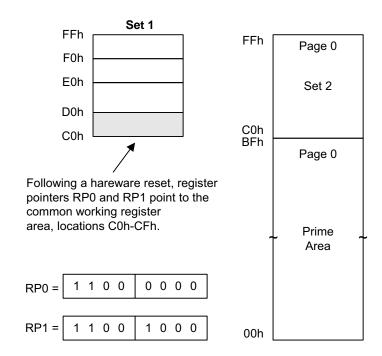

After a reset, RP0 and RP1 always point to the 16-byte common area in Set1 (C0h-CFh). Figure 17 illustrates the 8-byte working register areas (i.e., slices).

Figure 17. 8-Byte Working Register Areas

# 2.2.6. Using the Register Pointers

Register pointers RP0 and RP1, mapped to addresses D6h and D7h in Set1, are used to select two movable 8-byte working register slices in the register file. After a reset, they point to the working register common area: RP0 points to addresses C0h-C7h, and RP1 points to addresses C8h-CFh.

To change a register pointer value, load a new value to RP0 and/or RP1 using an SRP or LD instruction; see Figures 18 and 19.

Figure 18. Contiguous 16-Byte Working Register Block

Figure 19. Noncontiguous 16-Byte Working Register Block

With working register addressing, only access those two 8-bit slices of the register file that are currently pointed to by RP0 and RP1. Register pointers cannot, however, be used to select working register spaces in Set2, C0h to FFh, because these locations can be accessed only using the Indirect Register or Indexed Addressing modes.

The selected 16-byte working register block usually consists of two contiguous 8-byte slices. As a general programming guideline, Zilog recommends that RP0 point to the lower slice and RP1 point to the upper slice; see <u>Figure 17</u> on page 28. In some cases, it can be necessary to define working register areas in different (i.e., noncontiguous) areas of the register file. In Figure 18, RP0 points to the *upper* slice and RP1 to the *lower* slice.

Because a register pointer can point to the either of the two 8-byte slices in the working register block, define the working register area very flexibly to support program requirements, as indicated in the following two examples.

#### **Setting the Register Pointers**

```

SRP #70h ; RP0 \leftarrow 70h, RP1 \leftarrow 78h

SRP1 #48h ; RP0 \leftarrow no change, RP1 \leftarrow 48h,

SRP0 #0A0h ; RP0 \leftarrow A0h, RP1 \leftarrow no change

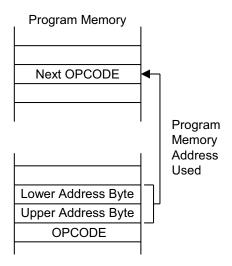

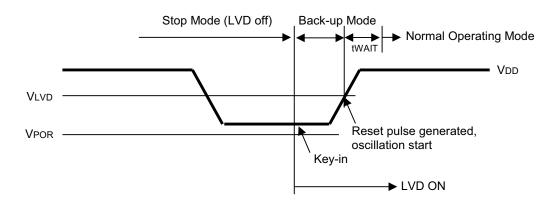

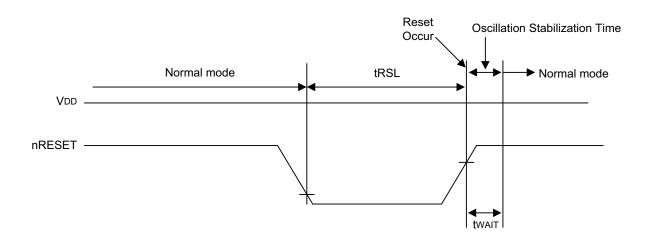

CLR RP0 ; RP0 \leftarrow 00h, RP1 \leftarrow no change