## S3FN60D

## **USB Remote 32-bit MCU**

Revision 1.30 January 2012

## **User's Manual**

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

© 2012 Samsung Electronics Co., Ltd. All rights reserved.

### **Important Notice**

Samsung Electronics Co. Ltd. ("Samsung") reserves the right to make changes to the information in this publication at any time without prior notice. All information provided is for reference purpose only. Samsung assumes no responsibility for possible errors or omissions, or for any consequences resulting from the use of the information contained herein.

This publication on its own does not convey any license, either express or implied, relating to any Samsung and/or third-party products, under the intellectual property rights of Samsung and/or any third parties.

Samsung makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Samsung assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation any consequential or incidental damages.

Customers are responsible for their own products and applications. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts.

Samsung products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Samsung product could reasonably be expected to create a situation where personal injury or death may occur. Customers acknowledge and agree that they are solely responsible to meet all other legal and regulatory requirements regarding their applications using Samsung products notwithstanding any information provided in this publication. Customer shall

Copyright © 2012 Samsung Electronics Co., Ltd.

Samsung Electronics Co., Ltd. San #24 Nongseo-Dong, Giheung-Gu Yongin-City, Gyeonggi-Do, Korea 446-711

Contact Us: <u>ms3535.jeong@samsung.com</u> TEL: (82)-(31)-209-3042 FAX: (82)-(31)-8000-2005

Home Page: http://www.samsungsemi.com

indemnify and hold Samsung and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim (including but not limited to personal injury or death) that may be associated with such unintended, unauthorized and/or illegal use.

**WARNING** No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written consent of Samsung. This publication is intended for use by designated recipients only. This publication contains confidential information (including trade secrets) of Samsung protected by Competition Law, Trade Secrets Protection Act and other related laws, and therefore may not be, in part or in whole, directly or indirectly publicized, distributed, photocopied or used (including in a posting on the Internet where unspecified access is possible) by any unauthorized third party. Samsung reserves its right to take any and all measures both in equity and law available to it and claim full damages against any party that misappropriates Samsung's trade secrets and/or confidential information.

**警**告本文件Q向经韩国三星电子株式会社授权的人员提供,其内容含有商业秘密保护相关法规规定并受其保护的三星电子株式会社商业秘密,任何直接或间接非法向第三人披露、传播、复制或允许第三人使用该文件全部或部分内容的行为(包括在互联网等公开媒介刊登该商业秘密而可能导致不特定第三人获取相关信息的行为)皆为法律严格禁止。此等违法行为一经发现,三星电子株式会社有权根据相关法规对其采取法律措施,包括但不限于提出损害赔偿请求。

## Trademarks

All brand names, trademarks and registered trademarks belong to their respective owners.

- Exynos, Exynos4210, FlexOneNAND, and OneNAND are trademarks of Samsung Electronics.

- ARM, Jazelle, TrustZone, and Thumb are registered trademarks of ARM Limited. Cortex, ETM, ETB, Coresight, ISA, and Neon are trademarks of ARM Limited.

- Java is a trademark of Sun Microsystems, Inc.

- SD is a registered trademark of Toshiba Corporation.

- MMC and eMMC are trademarks of MultiMediaCard Association.

- JTAG is a registered trademark of JTAG Technologies, Inc.

- Synopsys is a registered trademark of Synopsys, Inc.

- I2S is a trademark of Phillips Electronics.

- I<sup>2</sup>C is a trademark of Phillips Semiconductor Corp.

- MIPI and Slimbus are registered trademarks of the Mobile Industry Processor Interface (MIPI) Alliance.

All other trademarks used in this publication are the property of their respective owners.

## **Chip Handling Guide**

#### **Precaution against Electrostatic Discharge**

When handling semiconductor devices, be sure that the environment is protected against static electricity.

- 1. Operators should wear anti-static clothing and use earth band.

- 2. All objects that come in direct contact with devices should be made of materials that do not produce static electricity that would cause damage.

- 3. Equipment and work table must be earthed.

- 4. Ionizer is recommended to remove electron charge.

#### Contamination

Be sure to use semiconductor products in the environment that may not be exposed to dust or dirt adhesion.

#### **Temperature/Humidity**

Semiconductor devices are sensitive to environment temperature and humidity. High temperature or humidity may deteriorate semiconductor device's characteristics. Therefore avoid storage or use in such conditions.

#### **Mechanical Shock**

Care should be exercised not to apply excessive mechanical shock or force on semiconductor device.

#### Chemical

Do not expose semiconductor device to chemical because reaction to chemical may cause deterioration of device characteristics.

#### **Light Protection**

In case of non-EMC (Epoxy Molding Compound) package, do not expose semiconductor IC to strong light. It may cause device's malfunction. (But, some special products which utilize the light or have security function are excepted from this guide)

#### Radioactive, Cosmic and X-ray

Semiconductor devices can be influenced by radioactive, cosmic ray or X-ray. Radioactive, cosmic and X-ray may cause soft error during device operation. Therefore semiconductor devices must be shielded under environment that may be exposed to radioactive, cosmic ray or X-ray.

#### EMS (Electromagnetic Susceptibility)

Note that semiconductor device's characteristics may be affected by strong electromagnetic wave or magnetic field during operation under insufficient PCB circuit design for EMS.

#### SAMSUNG ELECTRONICS

## **Table of Contents**

| 1 PRODUCT OVERVIEW                                                   | 1-1 |

|----------------------------------------------------------------------|-----|

| 1.1 Overview                                                         | 1_1 |

| 1.2 Feature                                                          |     |

| 1.3 Block Diagram                                                    |     |

| 1.4 Pin Assignments (64-Pin TQFP)                                    |     |

| 1.5 Pin Circuits                                                     |     |

| 2 ADDRESS SPACE                                                      | 2-1 |

| 2.1 Overview                                                         |     |

| 2.2 Memory Configuration in Cortex M0 Side                           |     |

| 2.3 Smart Option                                                     |     |

| 3 CORTEX-M0                                                          | 3-1 |

| 3.1 Overview                                                         |     |

| 3.2 Features                                                         |     |

| 3.3 Interfaces                                                       |     |

| 4 INTERRUPTS                                                         | 4-1 |

| 4.1 Overview                                                         |     |

| 4.2 Features                                                         |     |

| 4.3 Interrupt Sources & Interrupt Vector                             |     |

| 4.4 System Interrupt Vector                                          |     |

| 5 MEMORY MAP                                                         | 5-1 |

| 5.1 Overview                                                         |     |

| 5.2 Default Memory Map                                               |     |

| 5.3 Core & Peripheral Special Function Register Map                  |     |

| 6 INSTRUCTION SET                                                    | 6-1 |

| 6.1 Cortex-M0 Instruction Set Summary                                |     |

| 7 CLOCK CIRCUITS                                                     | 7-1 |

| 7.1 Overview                                                         |     |

| 7.2 Features                                                         | 7-1 |

| 7.2.1 System Clock Circuit                                           |     |

| 7.2.2 Power Supply Selection Circuit                                 |     |

| 7.2.3 PLL Clock Circuit                                              |     |

| 7.3 Block Diagram                                                    |     |

| 7.4 Clock Status during Power-down Modes                             |     |

| 7.5 Clock Control State Machine<br>7.6 Power Source Changing Circuit |     |

| 7.6.1 Power Supply Selection                                         |     |

| 7.7 PLL (Phase Locked Loop)                                          |     |

| 7.8 Change PLL Settings in Normal Operation Mode                     |     |

| 7.9 Power Management                                                 |     |

SAMSUNG

|    | 7.9.1 Power Modes                                        |      |

|----|----------------------------------------------------------|------|

|    | 7.9.2 Low Power Mode and Wake-Up                         |      |

|    | 7.9.3 Enter IDLE Mode                                    |      |

|    | 7.9.4 Exit IDLE Mode                                     |      |

|    | 7.9.5 Enter STOP Mode                                    |      |

|    | 7.9.6 Exit STOP Mode                                     |      |

|    | 7.10 Register Description                                |      |

|    | 7.10.1 Register Map Summary                              |      |

| 8  | RESET                                                    | 8-1  |

|    | 8.1 Overview                                             |      |

|    | 8.1.1 Reset Sources                                      |      |

|    | 8.1.2 Reset Mechanism                                    |      |

|    | 8.1.3 External Reset Pin                                 |      |

|    | 8.1.4 Watch Dog Timer Reset                              |      |

|    | 8.1.5 S/W Reset                                          |      |

|    | 8.1.6 LVD Reset                                          |      |

|    | 8.1.7 POR Reset (Internal Power-On Reset)                |      |

|    | 8.1.8 System Reset Operation                             |      |

|    | 8.1.9 Status Table of Back-Up Mode, Stop Mode, and Reset |      |

|    | 8.2 Register Description                                 |      |

|    | 8.2.1 Register Map Summary                               |      |

| 9  | I/O PORTS                                                | 9-1  |

|    | 9.1 Overview                                             | 9-1  |

|    | 9.2 Features                                             |      |

|    | 9.2.1 Port Control Description                           |      |

|    | 9.3 Register Description                                 |      |

|    | 9.3.1 Register Map Summary                               |      |

| 1( | 0 BASIC TIMER/WATCHDOG TIMER                             | 10-1 |

|    | 10.1 Overview                                            | 10-1 |

|    | 10.2 Features                                            |      |

|    | 10.2.1 Basic Timer Control Register (BTCON)              |      |

|    | 10.2.2 Basic Timer Function Description                  |      |

|    | 10.2.3 Basic Timer/Watchdog Timer Block Diagram          |      |

|    | 10.3 Register Description                                |      |

|    | 10.3.1 Register Map Summary                              |      |

| 11 | 1 COUNTER A                                              | 11-1 |

|    | 11.1 Overview                                            | 11-1 |

|    | 11.1.1 Feature                                           |      |

|    | 11.1.2 Pin Description                                   |      |

|    | 11.2 Functional Description                              |      |

|    | 11.2.1 Block Diagram                                     |      |

|    | 11.2.2 Counter A Pulse Width Calculations                |      |

|    | 11.2.3 Counter A Data Register Setting                   |      |

|    | 11.2.4 Counter A output Signal Waveform                  |      |

|    | 11.3 Register Description                                |      |

|    | 11.3.1 Register Map Summary                              |      |

|    |                                                          |      |

| 12 TIMER/COUNTER                                         |      |

|----------------------------------------------------------|------|

| 12.1 Overview                                            |      |

| 12.1.1 Features                                          |      |

| 12.1.2 Pin Description                                   |      |

| 12.2 Functional Description                              |      |

| 12.2.1 Block Diagram                                     |      |

| 12.2.2 Counter Size                                      |      |

| 12.2.3 Counter Clock                                     |      |

| 12.2.4 Debug Option                                      |      |

| 12.2.5 Overflow Mode                                     |      |

| 12.2.6 Period Mode                                       |      |

| 12.2.7 Interrupt                                         |      |

| 12.3 Register Description                                |      |

| 12.3.1 Register Map Summary                              |      |

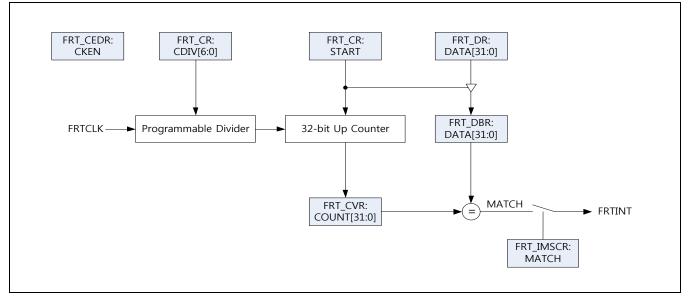

| 13 FREE RUNNING TIMER                                    | 13-1 |

| 13.1 Overview                                            |      |

| 13.1.1 Features                                          |      |

| 13.2 Functional Description                              |      |

| 13.2.1 Block Diagram                                     |      |

| 13.2.2 Timer Clock                                       |      |

| 13.2.3 Count and Data register                           |      |

| 13.2.4 Interrupt                                         |      |

| 13.2.5 Operation                                         |      |

| 13.3 Register Description<br>13.3.1 Register Map Summary |      |

| 14 SERIAL PERIPHERAL INTERFACE (SPI)                     |      |

| 14.1 Overview                                            |      |

| 14.1.1 Features                                          |      |

| 14.1.2 Operation                                         |      |

| 14.2 Register Description                                |      |

| 14.2.1 Register Map Summary                              |      |

| 15 UART                                                  |      |

| 15.1 Overview                                            |      |

| 15.2 Function Description                                |      |

| 15.2.1 Uart Operation                                    |      |

| 15.2.2 Data Transmission                                 |      |

| 15.2.3 Data Reception                                    |      |

| 15.2.4 Interrupt Request Generation                      |      |

| 15.2.5 DMA Operation                                     |      |

| 15.3 Baud Rate Generation                                |      |

| 15.3.1 Loop Back Mode                                    |      |

| 15.3.2 Infra Red (IrDA) Mode                             |      |

| 15.4 Register Description                                |      |

| 15.4.1 Register Map Summary                              | 15-8 |

|                                                          |      |

| 16 INTER-INTEGRATED CIRCUIT (IIC)                        | 16-1 |

| 16.1.1 Features                                                    |      |

|--------------------------------------------------------------------|------|

| 16.1.2 Pin Description                                             |      |

| 16.2 Functional Description                                        |      |

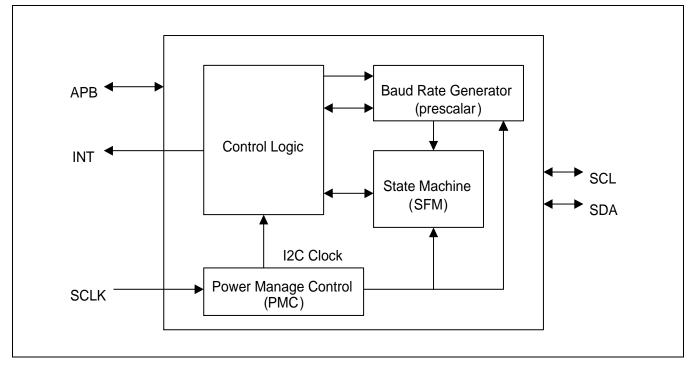

| 16.2.1 Block Diagram                                               |      |

| 16.2.2 Functional Operation                                        |      |

| 16.2.3 Extensions to the I2C-bus Specification<br>16.2.4 Fast Mode |      |

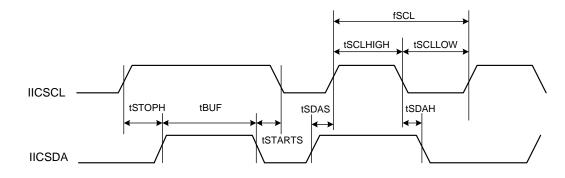

| 16.3 Inter-Intergrated Circuit Timing                              |      |

| 16.4 Register Description                                          |      |

| 16.4.1 Register Map Summary                                        |      |

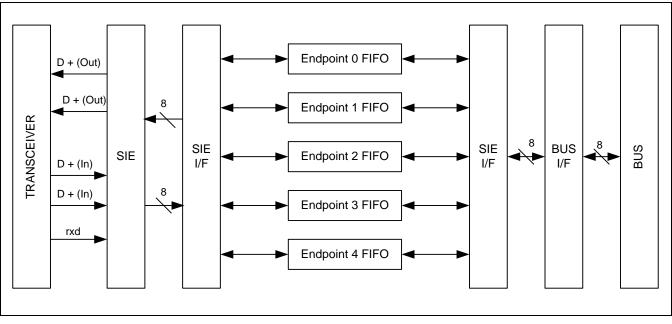

| 17 USB CONTROLLER                                                  | 17-1 |

| 17.1 Overview                                                      |      |

| 17.1.1 Features                                                    |      |

| 17.1.2 USB Block Overview                                          |      |

| 17.2 Register Description                                          |      |

| 17.2.1 Register Map Summary                                        |      |

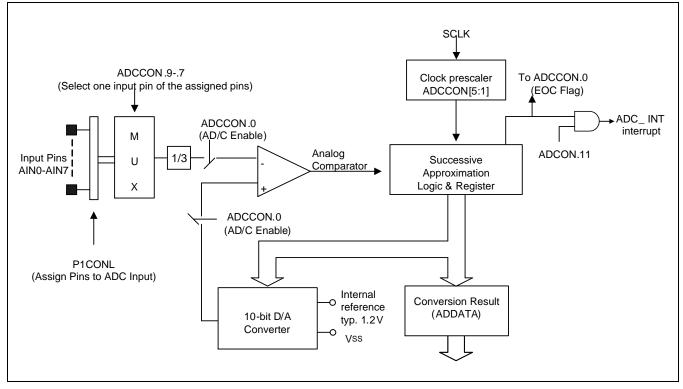

| 18 10-BIT ANALOG-TO-DIGITAL CONVERTER                              | 18-1 |

| 18.1 Overview                                                      |      |

| 18.1.1 Features                                                    |      |

| 18.1.2 Pin Description                                             |      |

| 18.2 Functional Description                                        |      |

| 18.2.1 Analog Input Type & Range                                   |      |

| 18.2.2 Reference Voltage                                           |      |

| 18.2.3 Power down Mode                                             |      |

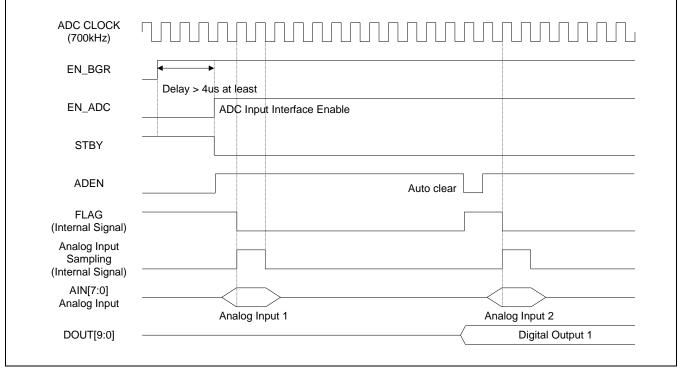

| 18.2.4 Wake-up Time                                                |      |

| 18.2.5 Digital Output Format                                       |      |

| 18.2.6 Input/Output Chart<br>18.2.7 Conversion Timing              |      |

| 18.2.8 End of Conversion                                           |      |

| 18.2.9 A/D Converter Control Register (ADCCON)                     |      |

| 18.3 Functional Block Diagram                                      |      |

| 18.4 Timing Diagram                                                |      |

| 18.5 Register Description                                          |      |

| 18.5.1 Register Map Summary                                        |      |

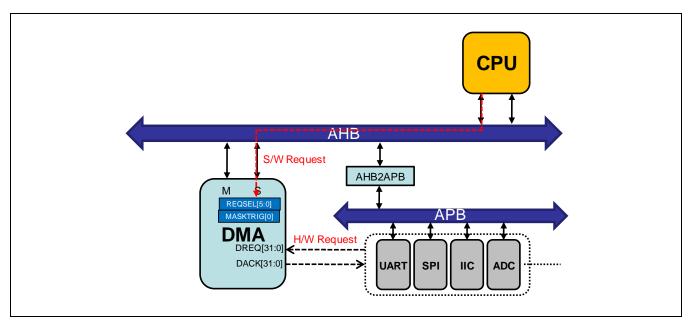

| 19 DMA (DIRECT MEMORY ACCESS)                                      | 19-1 |

| 19.1 Overview                                                      |      |

| 19.2 DMA Operation                                                 |      |

| 19.2.1 DMA Transfers                                               |      |

| 19.2.2 Starting/Ending DMA Transfers                               |      |

| 19.3 Operation Mode-H/W Request                                    |      |

| 19.3.1 Single Service Mode                                         |      |

| 19.3.2 Continuous Service Mode                                     |      |

| 19.4 DMA Transfer Size                                             |      |

| 19.4.1 Single Transfer Size                                        |      |

| 19.4.2 Burst (4-unit) Transfer Size                                |      |

| 19.5 DMA Operation Sequence                                        |      |

| 19.5.1 S/W Request Sequence                                        |      |

| 19.5.2 H/W Request Sequence                                        |      |

| 19.6 Register Description                          |      |

|----------------------------------------------------|------|

| 19.6.1 Register Map Summary                        |      |

| 20 EMBEDDED FLASH MEMORY                           | 20-1 |

| 20.1 Overview                                      |      |

| 20.1.1 Flash ROM Configuration                     |      |

| 20.2 Register Description                          |      |

| 20.2.1 Register Map Summary                        |      |

| 20.3 Programming                                   |      |

| 21 MEMORY PROTECTION UNIT                          | 21-1 |

| 21.1 Overview                                      |      |

| 21.2 Feature                                       |      |

| 21.2.1 Region Definition                           |      |

| 21.2.2 Region to Region ACCESSBILITY               |      |

| 21.3 MPU Abort Cases                               |      |

| 21.3.1 Read Cases                                  |      |

| 21.3.2 Write Cases                                 |      |

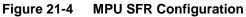

| 21.4 MPU SFR Configuration                         |      |

| 21.5 No Allowance Cases                            |      |

| 21.6 Register Description                          |      |

| 21.6.1 Register Map Summary                        |      |

| 22 LOW VOLTAGE DETECTOR                            | 22-1 |

| 22.1 Overview                                      |      |

| 22.2 LVD                                           |      |

| 22.2.1 LVD FLAG                                    |      |

| 22.3 Register Description                          |      |

| 22.3.1 Register Map Summary                        |      |

| 23 S3FN60D FLASH MCU                               | 23-1 |

| 23.1 Overview                                      |      |

| 23.1.1 Test Pin Voltage                            |      |

| 24 DEBUG                                           | 24-1 |

| 24.1 Overview                                      |      |

| 24.2 Feature                                       |      |

| 24.2.1 Block Diagram                               |      |

| 24.2.2 ARM Reference                               |      |

| 25 ELECTRICAL DATA                                 | 25-1 |

| 25.1 Overview                                      |      |

| 25.2 Absolute Maximum Ratings                      |      |

| 25.3 D.C. Electrical Characteristics               |      |

| 25.4 Characteristics of Low Voltage Detect Circuit |      |

| 25.5 LVD Enable Time                               |      |

| 25.6 A/D Converter Electrical Characteristics      |      |

| 25.7 Power on Reset Circuit                        |      |

| 25.8 Data Retention Supply Voltage in Stop Mode    |      |

| 25.9 Input/Output Capacitance                      |      |

| 25.10 Oscillation Characteristics                          |      |

|------------------------------------------------------------|------|

| 25.11 Ring Oscillator Characteristics                      |      |

| 25.12 Oscillation Stabilization Time                       |      |

| 25.13 AC Electrical Characteristics for Internal Flash ROM |      |

| 25.14 ESD Characteristics                                  |      |

| 25.15 USB DC Electrical Characteristics                    |      |

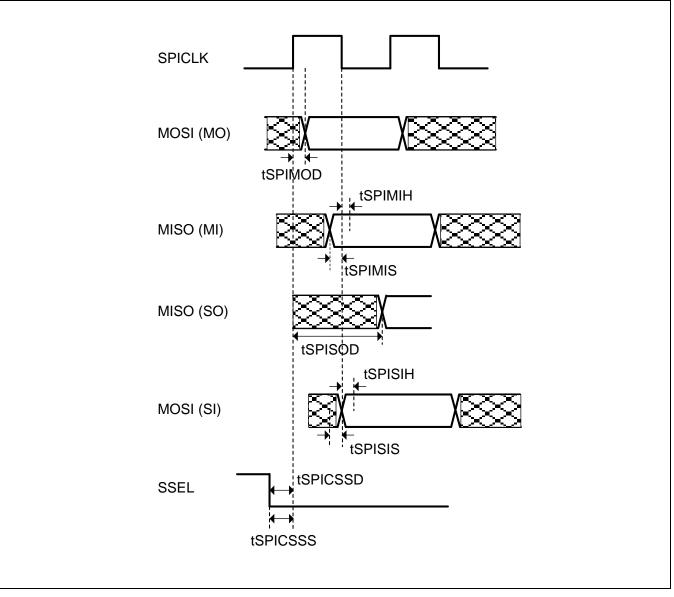

| 25.16 SPI Interface Transmit/Receive Timing Constants      |      |

| 25.17 IIC BUS Controller Module Signal Timing              |      |

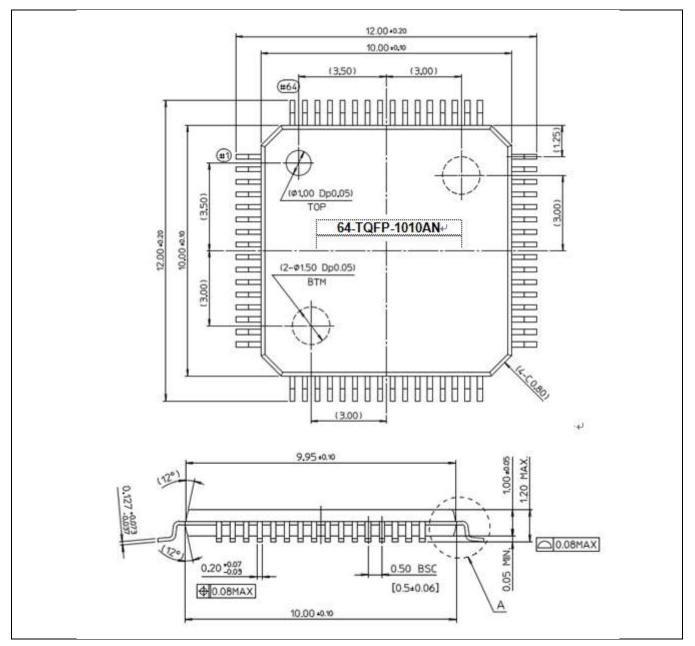

| 26 MECHANICAL DATA                                         | 26-1 |

| 26.1 Overview                                              |      |

## List of Figures

Title

| Number       |                                                                                 | Number |

|--------------|---------------------------------------------------------------------------------|--------|

| Figure 1-1   | Block Diagram                                                                   |        |

| Figure 1-2   | Pin Assignment Diagram (64-Pin TQFP Package)                                    |        |

| Figure 1-3   | External Interrupt Port to Wake Up Stop Mode (Pin Circuit Type 1)               | 1-10   |

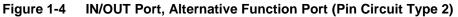

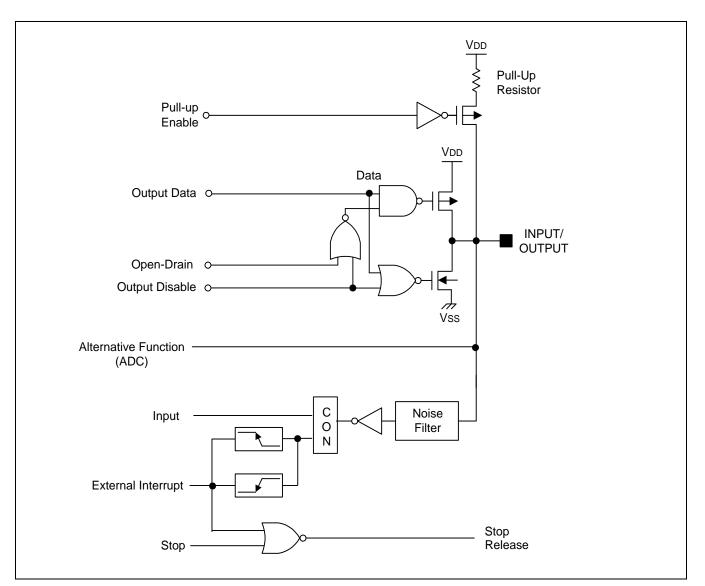

| Figure 1-4   | IN/OUT Port, Alternative Function Port (Pin Circuit Type 2)                     | 1-11   |

| Figure 1-5   | IN/OUT Port, Alternative Function Port & Ext. Interrupt (Pin Circuit Type 3)    | 1-12   |

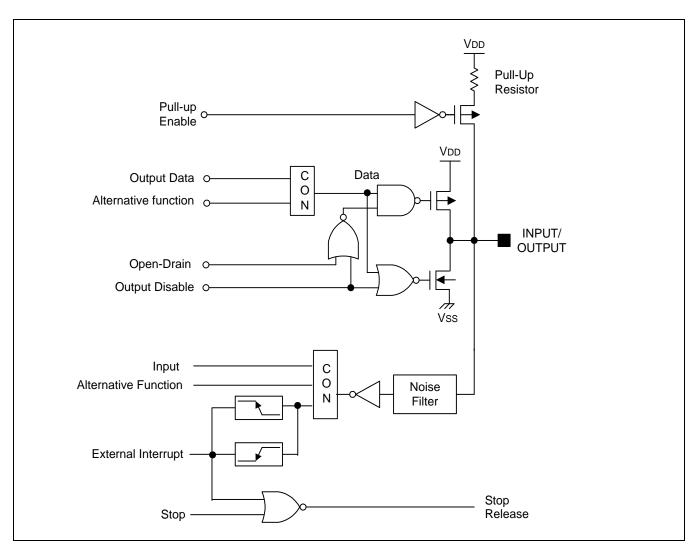

| Figure 1-6   | IN/OUT Port, Alternative Input Port (ADC) & Ext. Interrupt (Pin Circuit Type 4) | 1-13   |

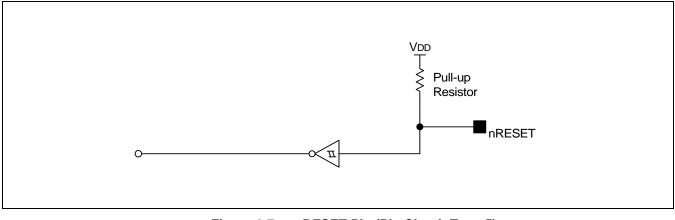

| Figure 1-7   | nRESET Pin (Pin Circuit Type 5)                                                 | 1-13   |

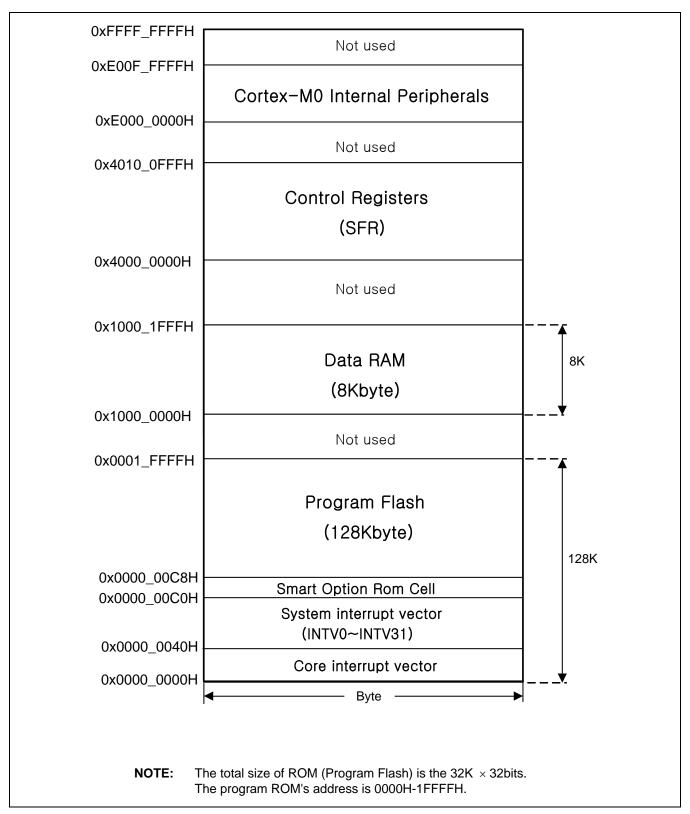

| Figure 2-1   | Program Memory Configuration                                                    | 2-2    |

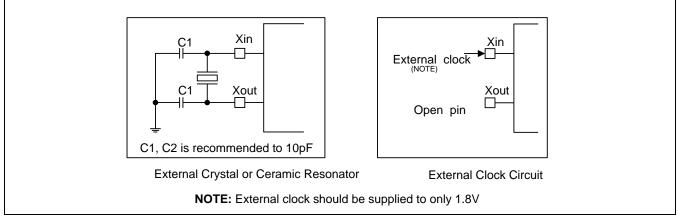

| Figure 7-1   | Main Oscillator Circuit                                                         |        |

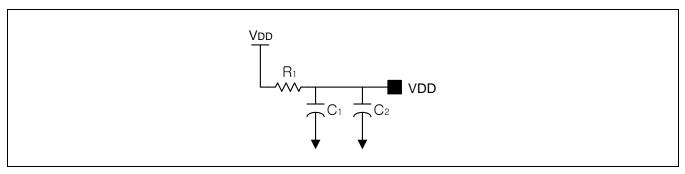

| Figure 7-2   | Power Circuit (V <sub>DD</sub> )                                                |        |

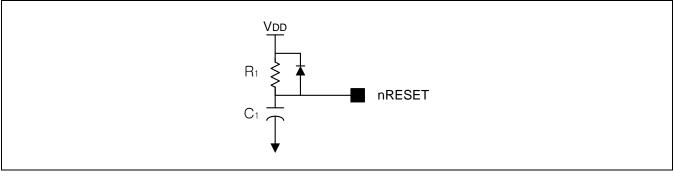

| Figure 7-3   | nRESET Circuit                                                                  |        |

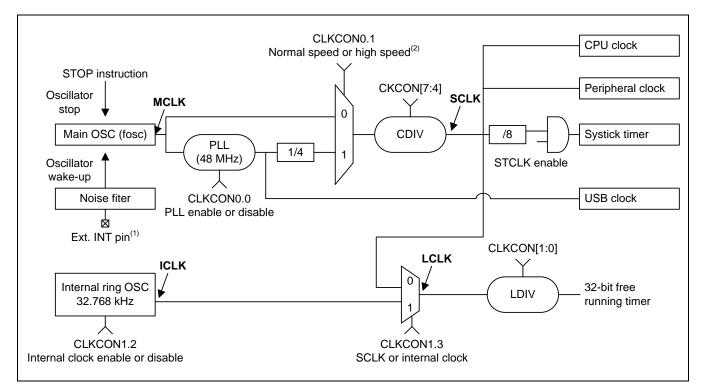

| Figure 7-4   | System Clock Circuit Diagram                                                    |        |

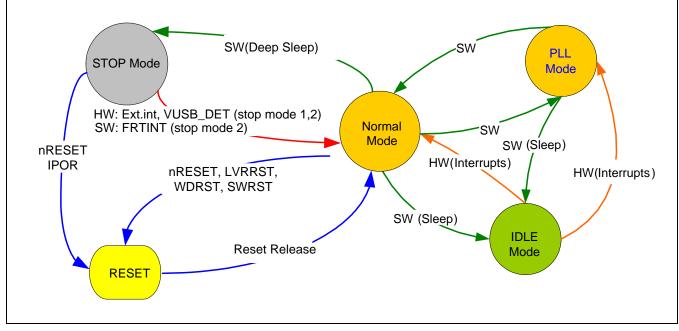

| Figure 7-5   | Clock Control State Machine                                                     |        |

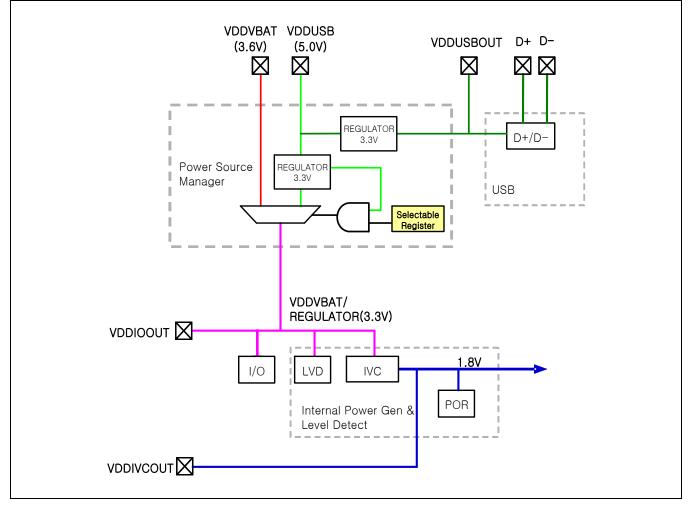

| Figure 7-6   | Power Source Changing Circuit                                                   |        |

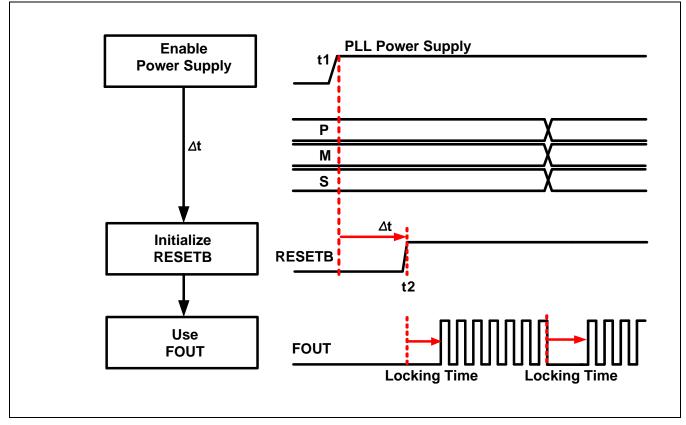

| Figure 7-7   | Timing Diagram of Clock Change in Normal Mode                                   |        |

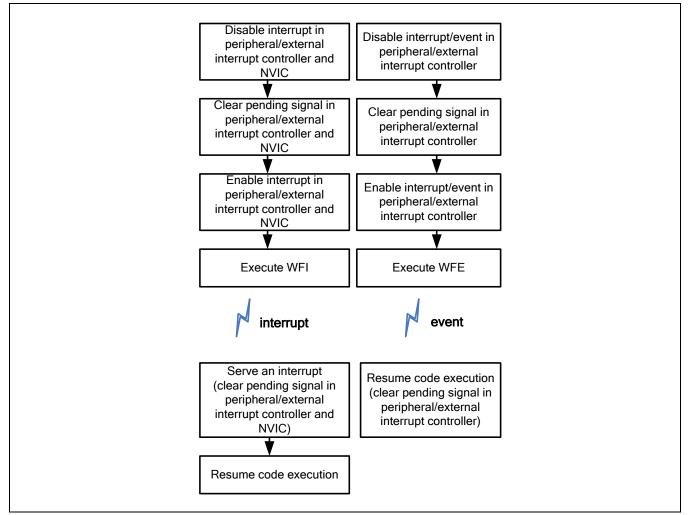

| Figure 7-8   | Different Handling Process for Interrupt and Event in Idle or Stop Mode         | 7-10   |

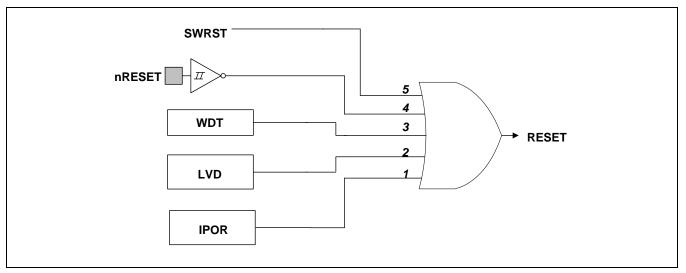

| Figure 8-1   | RESET Sources of The S3FN60D                                                    |        |

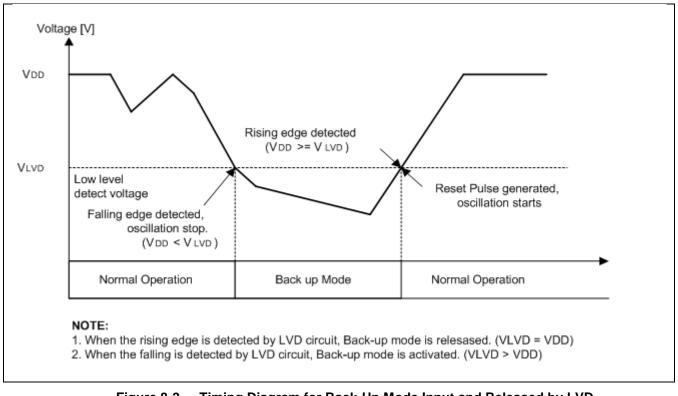

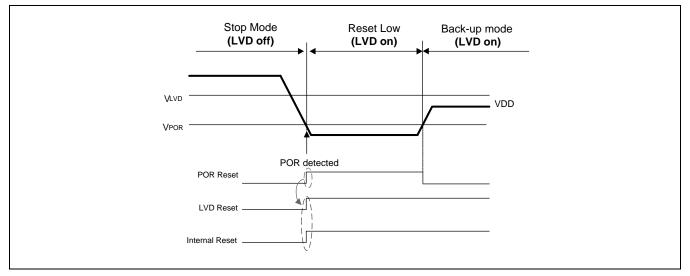

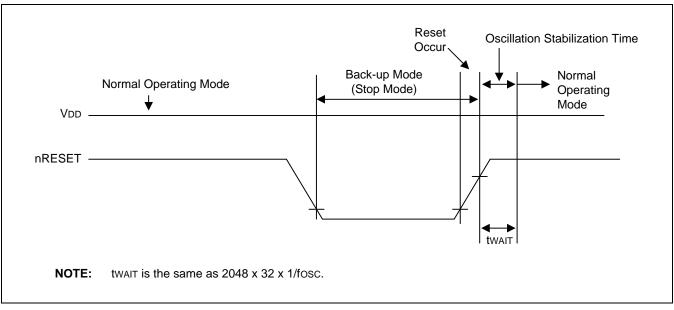

| Figure 8-2   | Timing Diagram for Back-Up Mode Input and Released by LVD                       |        |

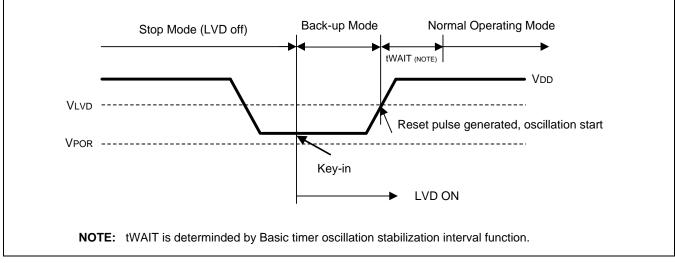

| Figure 8-3   | Timing Diagram in Stop Mode                                                     |        |

| Figure 8-4   | Timing Diagram in Stop Mode                                                     |        |

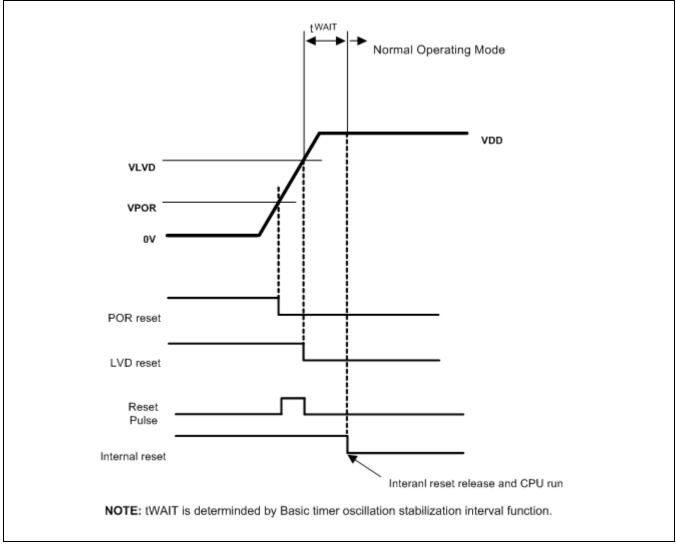

| Figure 8-5   | Timing Diagram for Internal Power-On Reset Circuit                              |        |

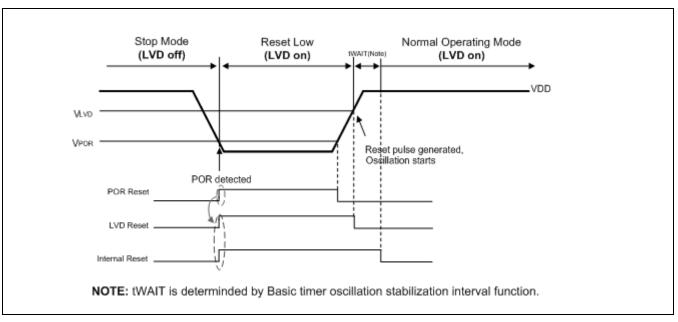

| Figure 8-6   | Reset Timing Diagram for the S3FN60D in STOP Mode by IPOR                       |        |

| Figure 8-7   | Wake Up in Stop Mode by IPOR (VPOR < VDD < VLVD)                                | 8-8    |

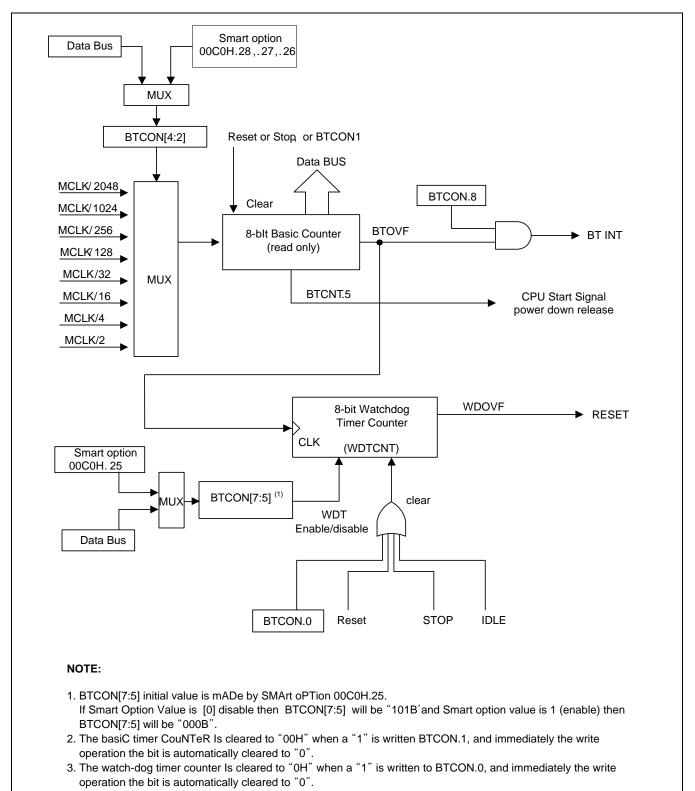

| Figure 10-1  | Basic Timer & Watchdog Timer Block Diagram                                      | 10-3   |

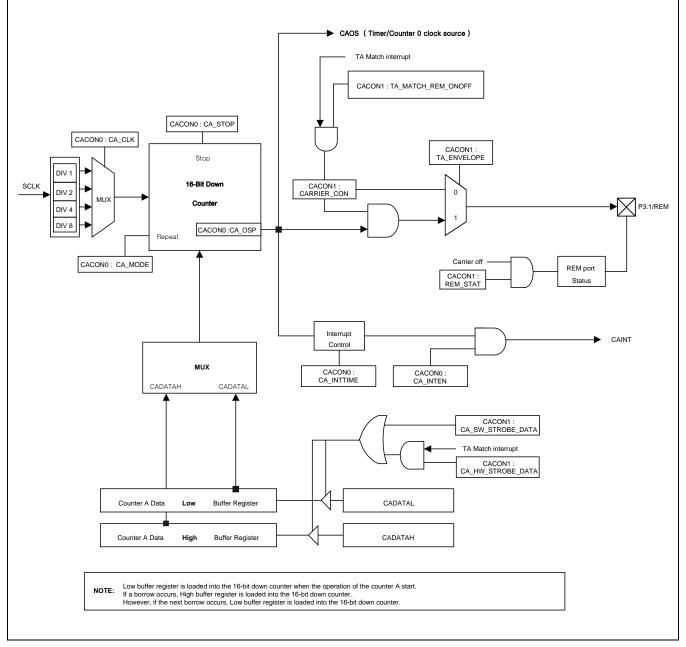

| Figure 11-1  | Counter A Block Diagram                                                         |        |

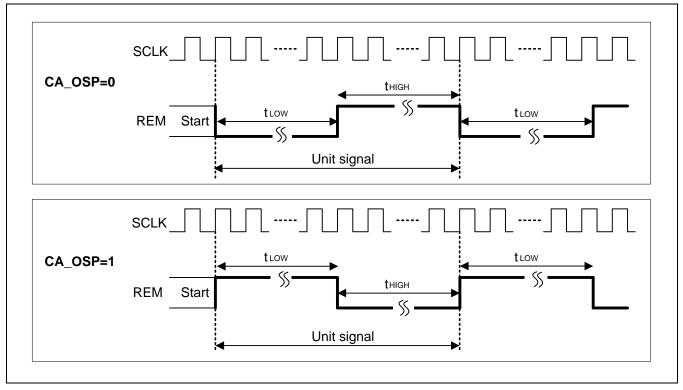

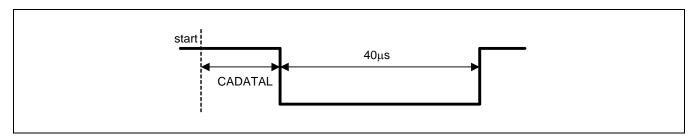

| Figure 11-2  | Counter A unit signal                                                           |        |

| Figure 11-3  | Counter A Block Diagram                                                         |        |

| Figure 11-4  | Counter A Output Flip-flop Waveforms in Repeat Mode                             |        |

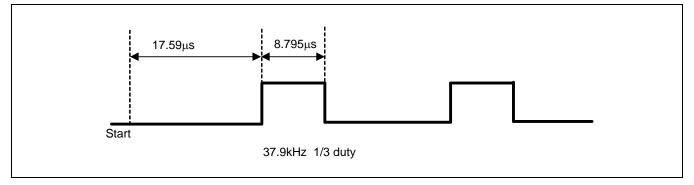

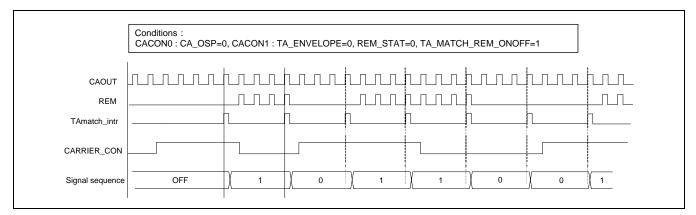

| Figure 11-5  | TA_EVELOPE = 0                                                                  |        |

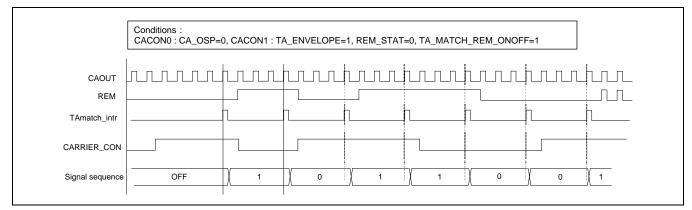

| Figure 11-6  | TA_ENVELOPE = 1                                                                 | 11-6   |

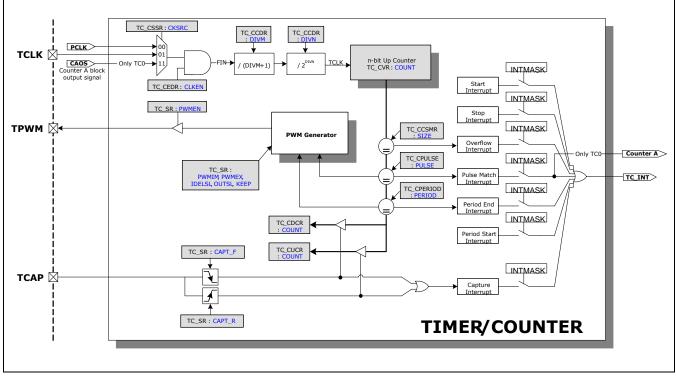

| Figure 12-1  | TC Block Diagram                                                                |        |

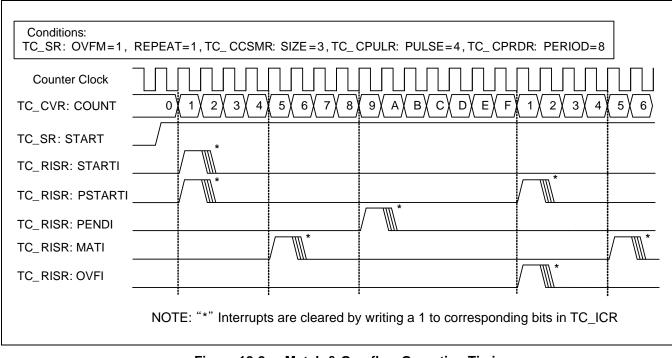

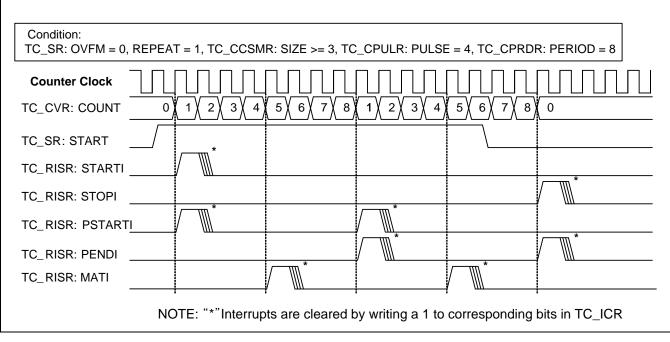

| Figure 12-2  | Match & Overflow Operation Timing                                               |        |

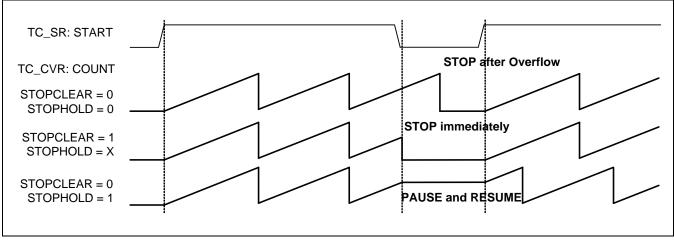

| Figure 12-3  | Counter Values According to START, STOPCLEAR and STOPHOLD                       |        |

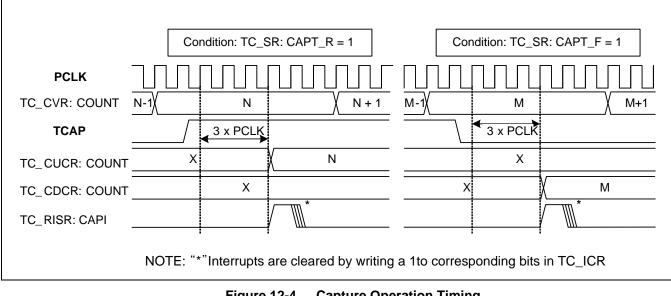

| Figure 12-4  | Capture Operation Timing                                                        |        |

| Figure 12-5  | Period Mode Timing                                                              |        |

| Figure 12-6  | Interval Operation                                                              |        |

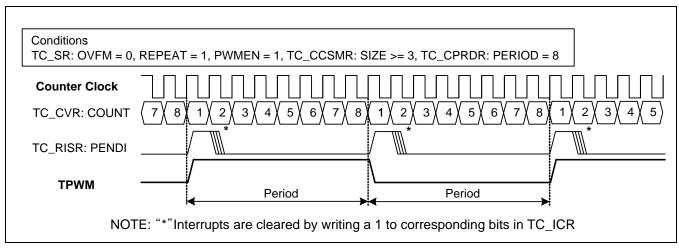

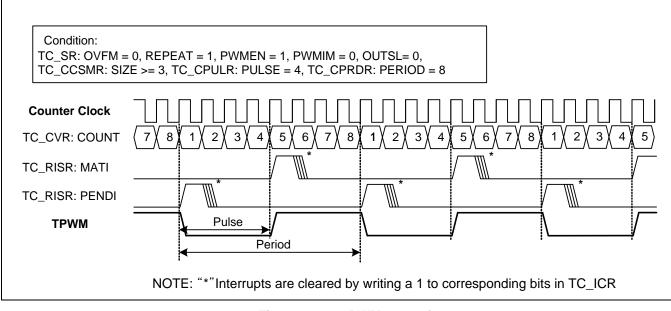

| Figure 12-7  | PWM Operation                                                                   |        |

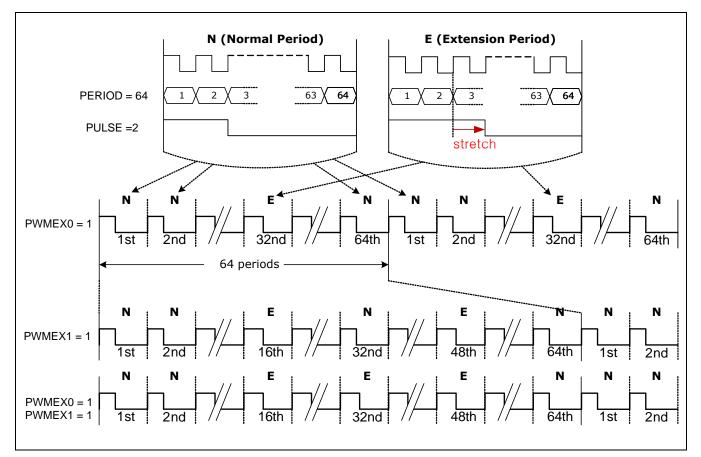

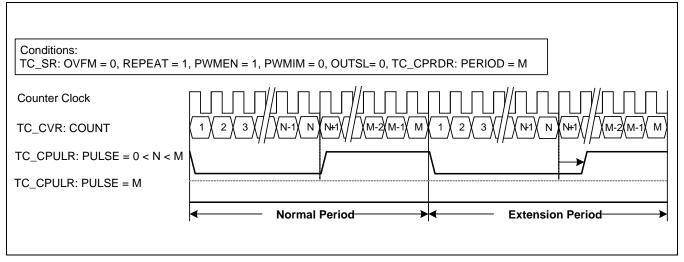

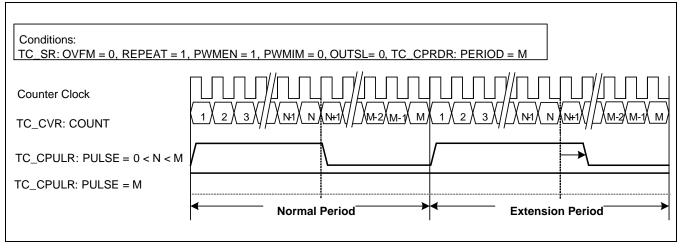

| Figure 12-8  | PWM Extension Waveform                                                          |        |

| Figure 12-9  | PWM Waveform with OUTSL = 0                                                     |        |

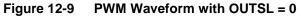

| Figure 12-10 | PWM Waveform with OUTSL = 1                                                     | 12-11  |

Figure

Page

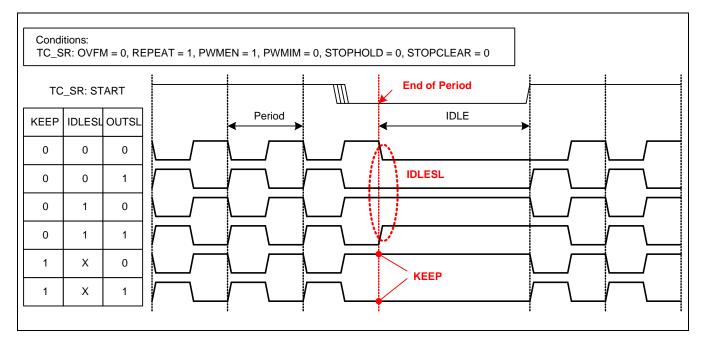

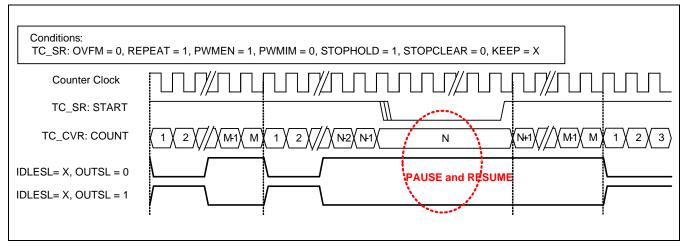

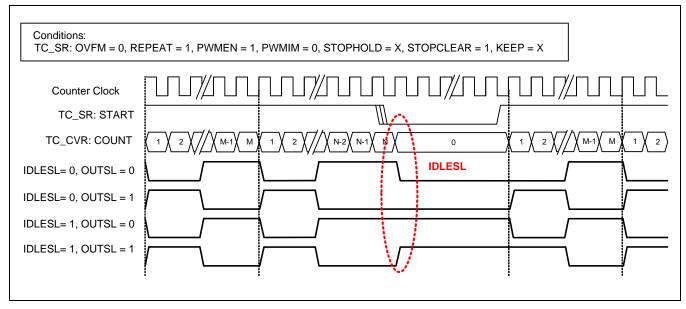

| Figure 12-11  | PWM Waveform Under IDLE State                                            | 12-12 |

|---------------|--------------------------------------------------------------------------|-------|

| Figure 12-12  | PWM Waveform with STOPHOLD = 1, STOPCLEAR = 0                            |       |

| Figure 12-13  | PWM Waveform with STOPCLEAR = 1                                          |       |

|               |                                                                          |       |

| Figure 13-1   | Free Running Timer Block Diagram                                         |       |

| Figure 13-2   | Simplified Timer Function Diagram: Match                                 |       |

|               |                                                                          |       |

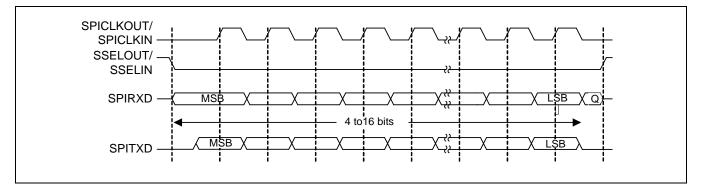

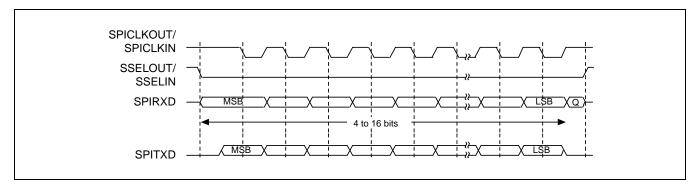

| Figure 14-1   | Motorola SPI Frame Format (Single Transfer) with SPO = 0 and SPH = 0     | 14-4  |

| Figure 14-2   | Motorola SPI Frame Format (Continuous Transfer) with SPO = 0 and SPH = 0 |       |

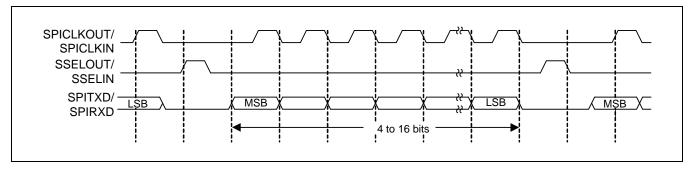

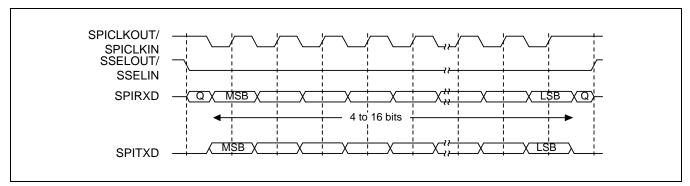

| Figure 14-3   | Motorola SPI Frame Format (Single Transfer) with SPO = 0 and SPH = 1     |       |

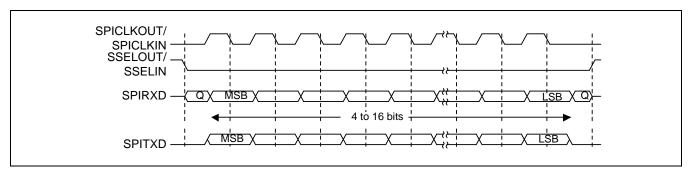

| Figure 14-4   | Motorola SPI Frame Format (Single Transfer) with SPO = 1 and SPH = 0     |       |

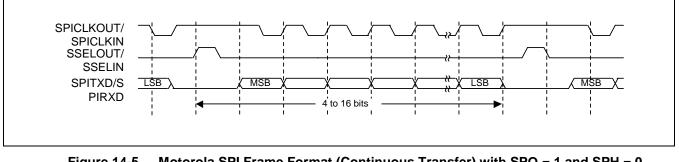

| Figure 14-5   | Motorola SPI Frame Format (Continuous Transfer) with SPO = 1 and SPH = 0 |       |

| Figure 14-5   | Motorola SPI Frame Format with SPO = 1 and SPH = 1                       |       |

| -             |                                                                          |       |

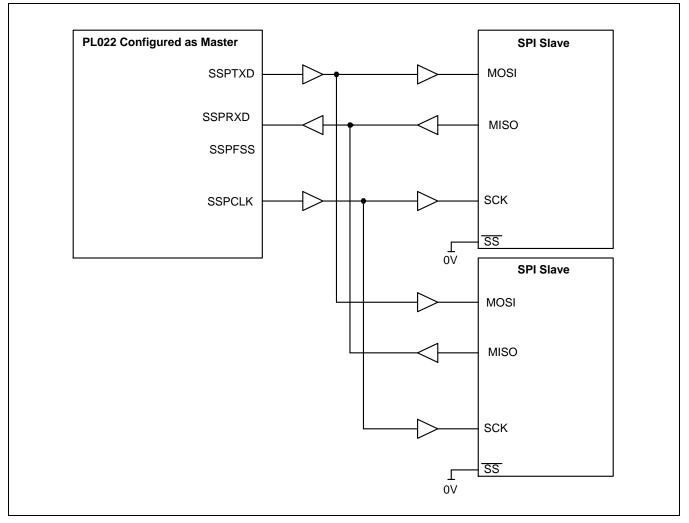

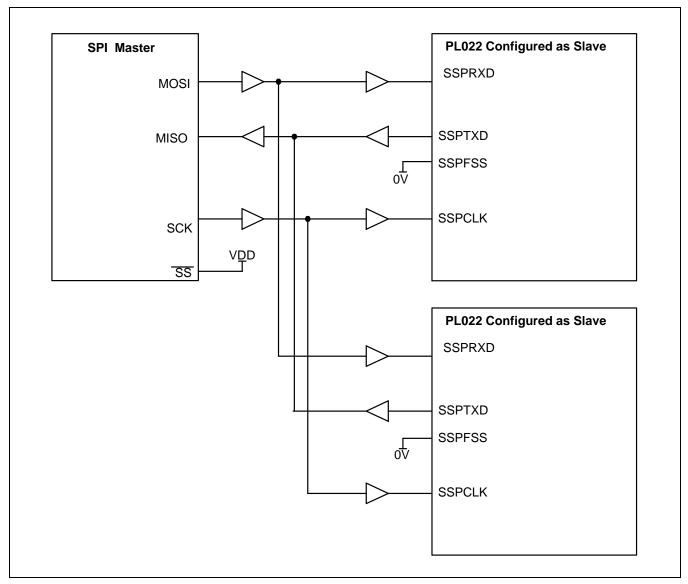

| Figure 14-7   | PrimeCell SSP Master Coupled To Two Slaves.                              |       |

| Figure 14-8   | SPI Master Coupled to two PrimeCell SSP Slaves                           | 14-11 |

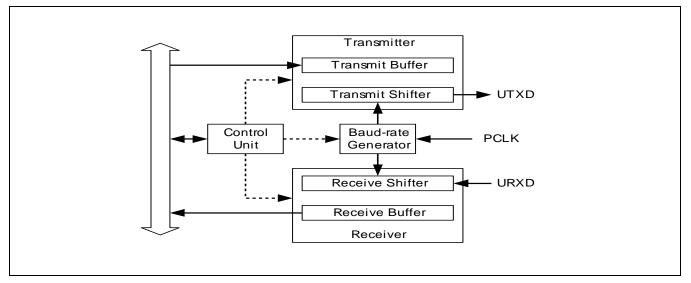

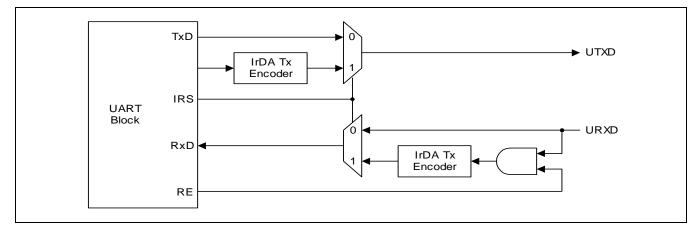

| Figure 15-1   | UART Block Diagram                                                       | 15-1  |

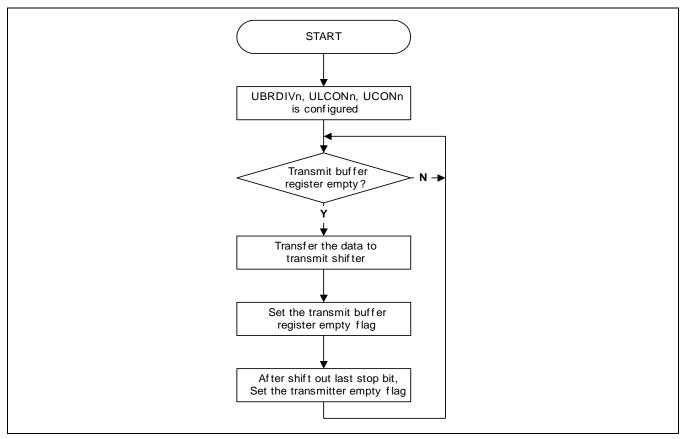

| Figure 15-2   | UART Data Transmission Process                                           |       |

|               |                                                                          |       |

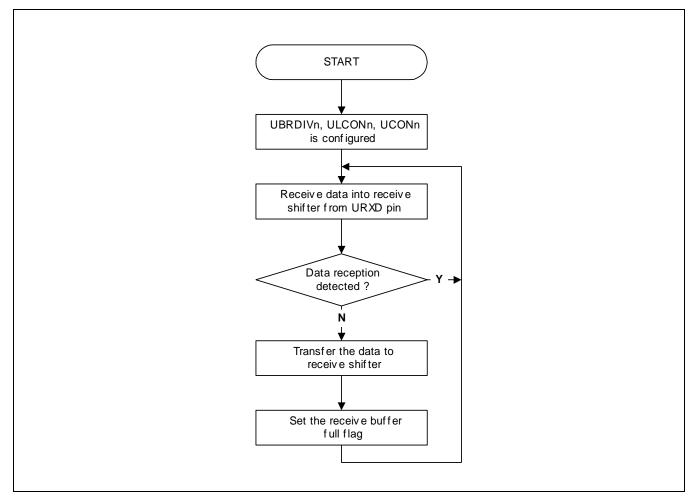

| Figure 15-3   | UART Data Reception Process                                              |       |

| Figure 15-4   | IrDA Function Block Diagram                                              |       |

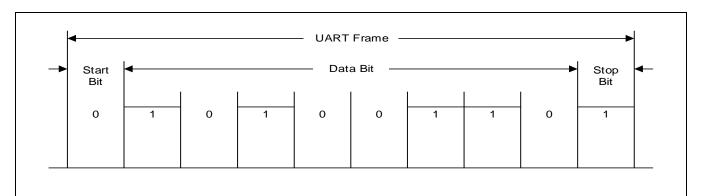

| Figure 15-5   | Serial I/O Frame Timing Diagram (Normal UART)                            |       |

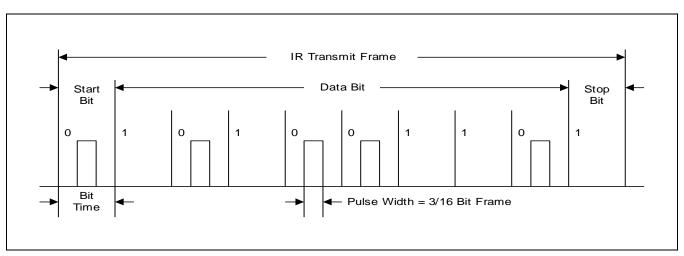

| Figure 15-6   | Infra Red (IrDA) Transmit Mode Frame Timing Diagram                      |       |

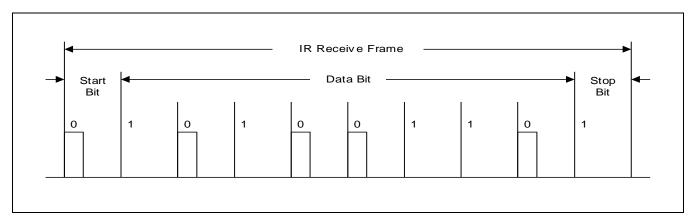

| Figure 15-7   | Infra Red (IrDA) Receive Mode Frame Timing Diagram                       | 15-7  |

|               |                                                                          | 40.0  |

| Figure 16-1   | Block Diagram                                                            |       |

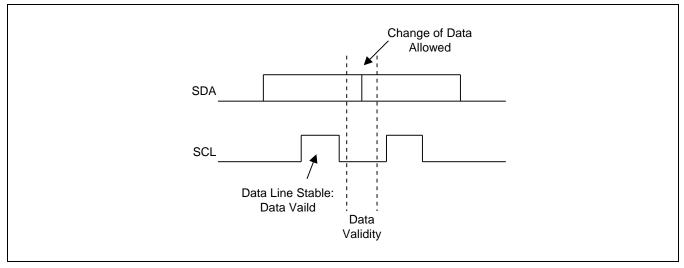

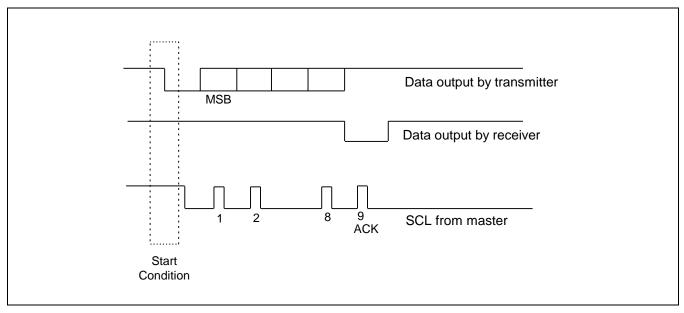

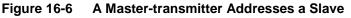

| Figure 16-2   | Data Validity                                                            |       |

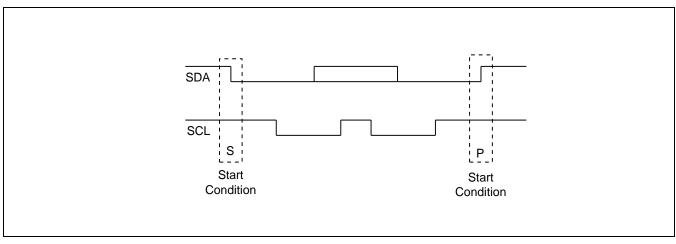

| Figure 16-3   | Start and Stop Conditions                                                |       |

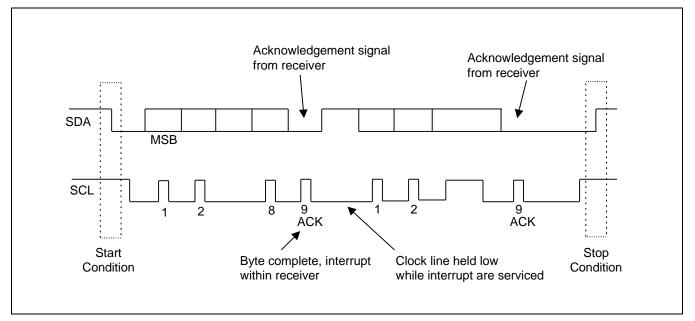

| Figure 16-4   | Data Transfer on the I2C Bus                                             |       |

| Figure 16-5   | Acknowledge                                                              |       |

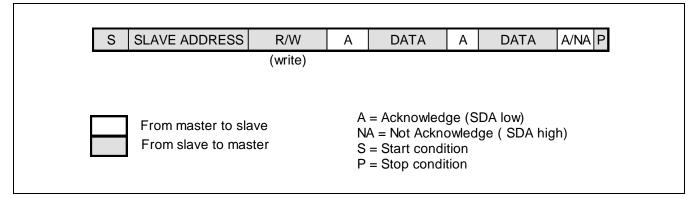

| Figure 16-6   | A Master-transmitter Addresses a Slave                                   |       |

| Figure 16-7   | Hold and Setup Delays                                                    | 16-43 |

| Figure 17-1   | USB Core Block Diagram                                                   | 17-3  |

| Figure 18-1   | A/D Converter Functional Block Diagram                                   | 18-4  |

| Figure 18-2   | A/D Conversion Phase                                                     |       |

| Figure 18-3   | A/D Converter Data Register (ADDATA)                                     |       |

| 9             |                                                                          |       |

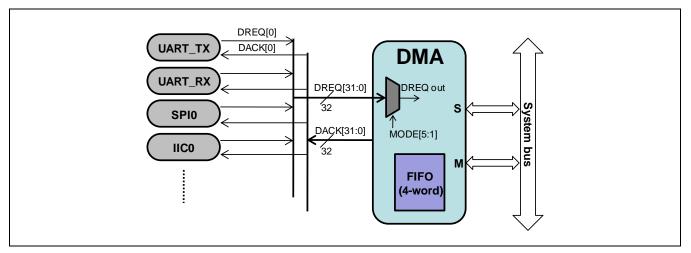

| Figure 19-1   | DMA Request Mode                                                         | 19-2  |

| Figure 19-2   | DMA Unit Block Diagram                                                   |       |

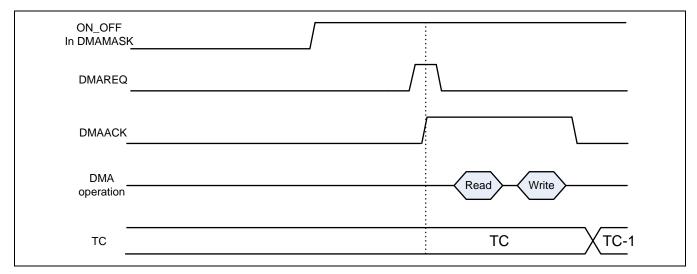

| Figure 19-3   | Single Transfer in Single Service Mode                                   |       |

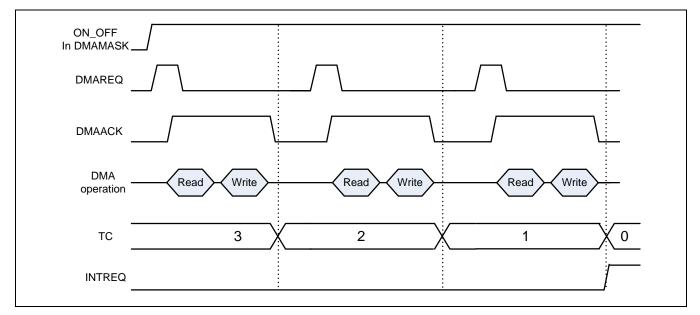

| Figure 19-4   | Sequential Transfer in Single Service Mode                               |       |

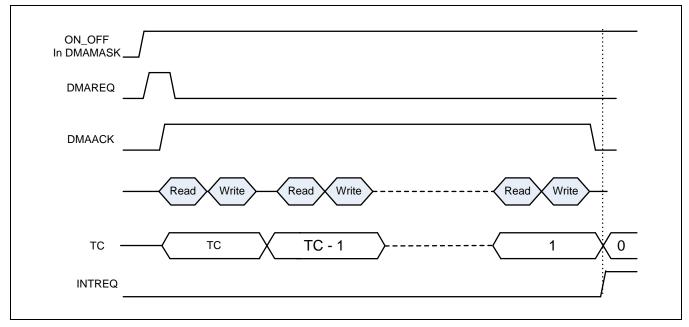

| Figure 19-5   | Continuous Service Mode                                                  |       |

| Figure 19-6   | Burst (4-unit) Transfer Size                                             |       |

| . goi e i e e |                                                                          |       |

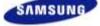

| Figure 20-1   | Sector Erase Flowchart in User Program Mode                              | 20-6  |

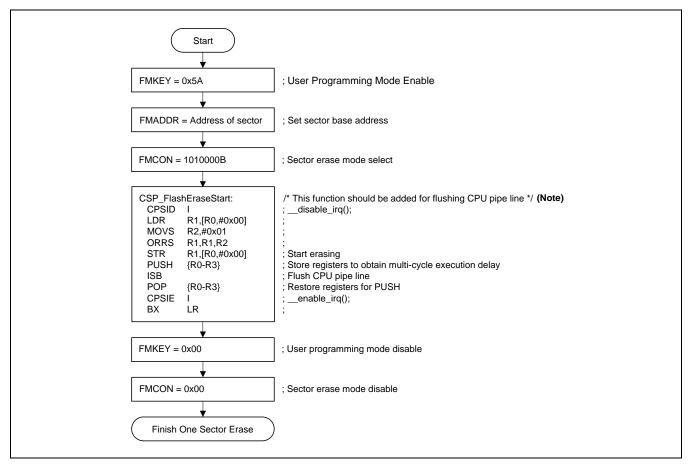

| Figure 20-2   | Page Erase Flowchart in User Program Mode                                |       |

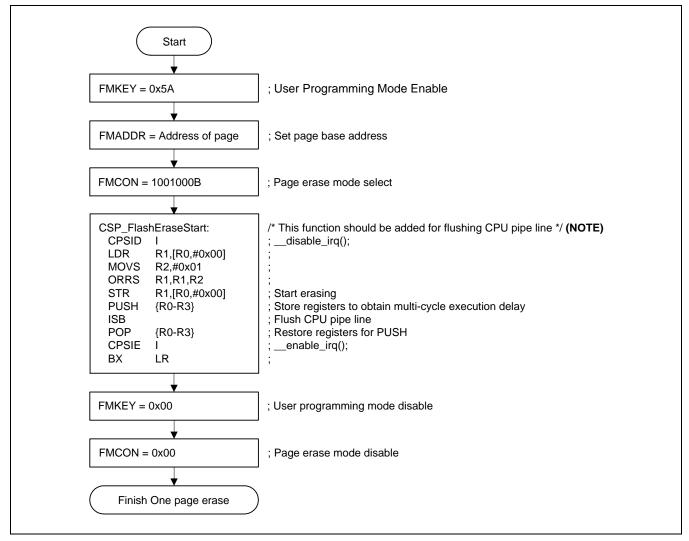

| Figure 20-3   | 1-word Program Flowchart in a User Program Mode                          |       |

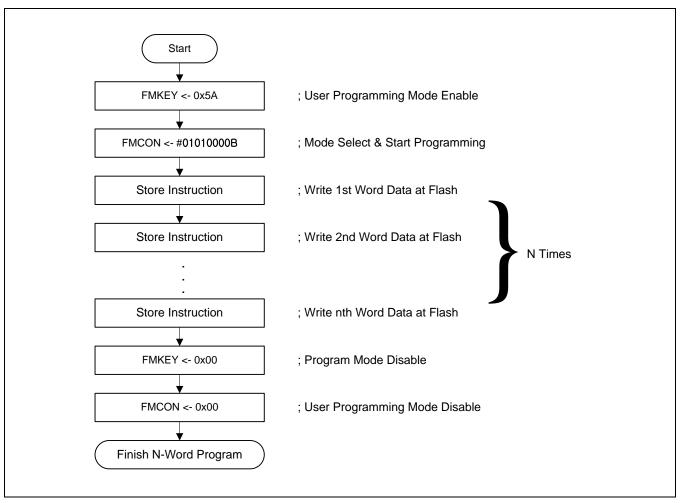

| Figure 20-4   | N-word Program Flowchart in a User Program Mode                          |       |

| 90.0 20 4     |                                                                          |       |

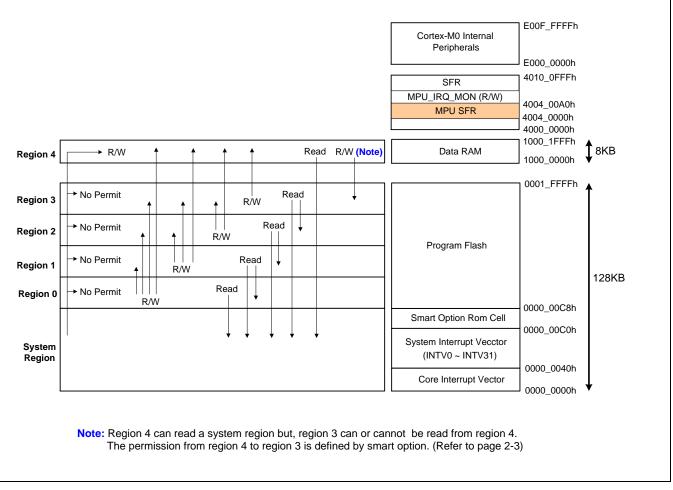

| Figure 21-1   | MPU Enabled Access Permission Configuration                              |       |

| Figure 21-2   | MPU Enabled Access Permission Configuration                              |       |

| Figure 21-3   | MPU Enabled Access Permission Configuration                              |       |

|               | in e Endeer loose remission comgaration                                  |       |

| Figure 21-4 | MPU SFR Configuration                                            | 21-9  |

|-------------|------------------------------------------------------------------|-------|

| Figure 21-5 | NO Allowance Case                                                | 21-10 |

| Figure 22-1 | Low Voltage Detect (LVD) Block Diagram                           | 22-3  |

| Figure 23-1 | S3FN60D Pin Assignment                                           | 23-1  |

| Figure 24-1 | Block Diagram                                                    |       |

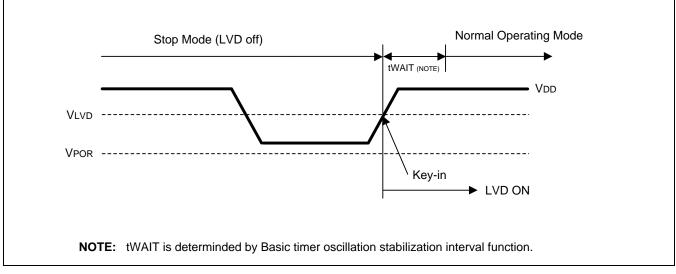

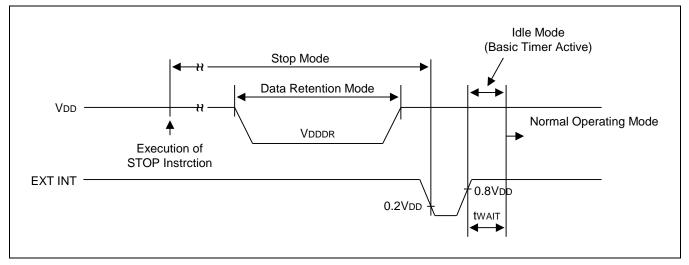

| Figure 25-1 | Stop Mode Release Timing when Initiated by an External Interrupt |       |

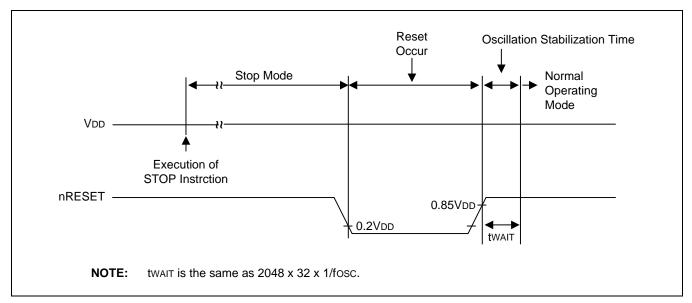

| Figure 25-2 | Stop Mode Release Timing when Initiated by a Reset               |       |

| Figure 25-3 | Stop Timing Diagram for Back-up Mode Input in Stop Mode          |       |

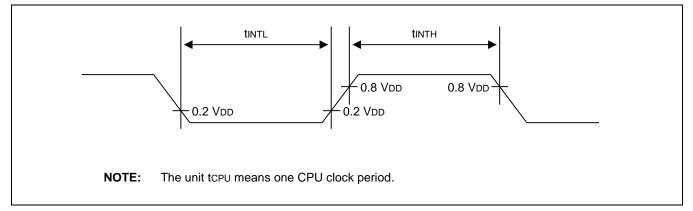

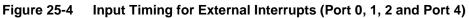

| Figure 25-4 | Input Timing for External Interrupts (Port 0, 1, 2 and Port 4)   |       |

| Figure 25-5 | Input Timing for Reset (nRESET Pin)                              |       |

| Figure 25-6 | SPI Interface Transmit/Receive Timing Constants                  |       |

| Figure 26-1 | 64-Pin TQFP Package Dimension                                    |       |

|             |                                                                  |       |

## List of Tables

| Table Title Number                               |                                                                                                                   | Page<br>Number |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------|--|

| Table 1-1                                        | Pin Descriptions of 64-TQFP                                                                                       |                |  |

| Table 4-1<br>Table 4-2                           | Core Exception Vector<br>System Interrupt Vectors & Sources                                                       |                |  |

| Table 5-1<br>Table 5-2<br>Table 5-3<br>Table 5-4 | S3FN60D's Memory Map<br>Core Special Function Register Map<br>Peripheral Memory Map<br>Memory Map of SFR          |                |  |

| Table 6-1                                        | Cortex-M0 Instruction Summary                                                                                     |                |  |

| Table 8-1<br>Table 8-2                           | Reset Condition in STOP Mode<br>Summary of Each Mode                                                              |                |  |

| Table 11-1                                       | Pin Description                                                                                                   | 11-1           |  |

| Table 12-1<br>Table 12-2<br>Table 12-3           | Pin Description<br>PWM Extension Bits<br>PWM Output Polarity According to Control Bits                            |                |  |

| Table 15-1                                       | Baud Rate Table                                                                                                   | 15-17          |  |

| Table 16-1<br>Table 16-2                         | S3FN60D Pin Description<br>Examples of Baud Rate Configuration                                                    |                |  |

| Table 16-3<br>Table 16-4<br>Table 16-5           | Definition of Bytes in First Byte<br>Timing Requirements<br>Values of FSCL in kHz Depending of PRV, FAST and SCLK |                |  |

| Table 16-6<br>Table 16-7                         | Master/Receiver Mode Status Codes                                                                                 |                |  |

| Table 16-8<br>Table 16-9<br>Table 16-10          | Slave/Receiver Mode Status Codes<br>Slave/Transmitter Mode Status Codes<br>Miscellaneous Status Codes             |                |  |

| Table 18-1                                       | ADC Pin Description                                                                                               |                |  |

| Table 21-1                                       | Region Definition                                                                                                 |                |  |

| Table 21-2<br>Table 21-3                         | Region Accessibility<br>Region Accessibility                                                                      |                |  |

| Table 21-4                                       | MPU Abort Cases                                                                                                   |                |  |

| Table 21-5                                       | Abort Occurrences DURING Reading Smart Option 0                                                                   |                |  |

| Table 21-6                                       | Abort Occurrences DURING Reading Smart Option 1                                                                   |                |  |

| Table 21-7<br>Table 21-8                         | Abort Occurrences DURING Writing Smart Option 0<br>Abort Occurrences DURING Writing Smart Option 1                |                |  |

| Table 22-1                                       | Characteristics of Low Voltage Detect Circuit                                                                     |                |  |

| Table 22-2  | LVD Enable Time                                       | 22-3 |

|-------------|-------------------------------------------------------|------|

| Table 23-1  | Descriptions of Pins Used to Read/Write the Flash ROM |      |

| Table 25-1  | Absolute Maximum Ratings                              |      |

| Table 25-2  | D.C. Electrical Characteristics                       |      |

| Table 25-3  | Characteristics of Low Voltage Detect Circuit         |      |

| Table 25-4  | LVD Enable Time                                       |      |

| Table 25-5  | A/D Converter Electrical Characteristics              |      |

| Table 25-6  | Power On Reset Circuit                                |      |

| Table 25-7  | Data Retention Supply Voltage in Stop Mode            |      |

| Table 25-8  | Input/Output Capacitance                              |      |

| Table 25-9  | Oscillation Characteristics                           |      |

| Table 25-10 | Ring Oscillator Characteristics                       |      |

| Table 25-11 | Oscillation Stabilization Time                        |      |

| Table 25-12 | AC Electrical Characteristics for Internal Flash ROM  |      |

| Table 25-13 | ESD Characteristics                                   |      |

| Table 25-14 | USB DC Electrical Characteristics                     |      |

| Table 25-15 | SPI Interface Transmit/Receive Timing Constants       |      |

| Table 25-16 | IIC BUS Controller Module Signal Timing               |      |

# Product Overview

#### 1.1 Overview

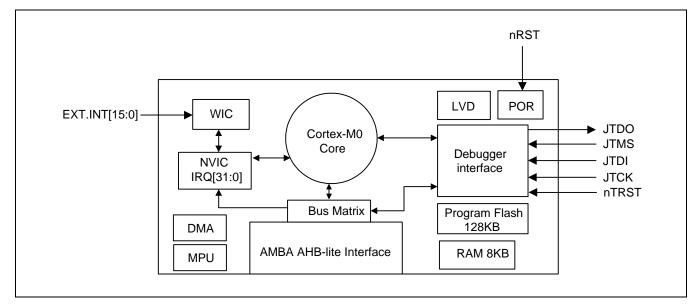

The S3FN60D single-chip CMOS micro-controller is specially designed and packaged for "USB Remote controller" application. The S3FN60D is a family of the smallest and lowest power processor with Cortex-M0 designed by Advanced RISC Machines (ARM). The S3FN60D has 128 Kbytes flash memory, 8 Kbytes data memory.

The following is the list of integrated on-chip functions that are described in detail in this user's manual:

- Internal LVD circuit and 32-bit-programmable pins for external interrupts

- One 8-bit basic timer for oscillation stabilization and watchdog function (System reset)

- Three variable timer/counters (16-bit, 32-bit etc.) with selectable operating modes

- One 16-bit counter with auto-reload function and one-shot or repeat control

- One 32-bit free running timer

- One channel UART

- Two channel 8-bit/16-bit/32-bit SPI

- Two channel IIC

- USB device 2.0 (12 Mbps full speed)

- One channel DMA controller

- Internal ring oscillator: 32.768 kHz

- Memory protection unit

- Crystal/Ceramic resonator or external clock can be used as the clock source and PLL

The S3FN60D is a versatile general-purpose microcontroller, which is especially suitable for use as remote transmitter controller. It is currently available in 64-pin TQFP package.

#### 1.2 Feature

#### CPU

• 32-bit RISC ARM cortextm-M0 core

#### Memory

- Program memory:

- 128 Kbyte internal flash memory

- 10 years data retention

- Endurance: 10,000 Erase/Program cycles

- 32-bit programmable

- Data memory: 8 Kbyte RAM

- Flash Erase Size: Page (256 byte) or sector (8 Kbyte)

#### I/O Ports

• Five 8-bit I/O ports (P0, P1, P2, P4, P5), One 7-bit I/O port (P3) and one 3-bit I/O port (P6) for a total of 50-bit programmable pins.

#### **Carrier Frequency Generator**

• One 16-bit counter with auto-reload function and one-shot or repeat control (Counter A)

#### **Basic Timer and Timer/Counters**

- One programmable 8-bit basic timer (BT) for oscillation stabilization control or watchdog timer (Software reset) function

- Three variable bit timer/counter (TA, T1, T2) with five operating modes: One-shot operation or repeated operation, Match & Overflow operation, Capture operation, Interval operation, PWM operation

- One 32-bit free running timer (FRT)

#### **Two Channel SPI**

• 8-bit/16-bit/32-bit programmable data length

#### One Channel UART

- 1-channel UART with interrupt-based operation or a DMA request

- Programmable baud rates

- Supports 5-bit, 6-bit, 7-bit and 8-bit serial data transmit/receive frame in UART

#### **Two Channel IIC**

• 2-channel I2C peripherals serial bus

#### **One Channel USB Device**

- 1-port USB device

- USB 2.0 full speed (12 Mbps)

#### **Memory Protection Unit**

- Read/write access controllable

- Base/Limit region registers: 4 sets

- Configurable range: 4 Mbytes areas with 256 byte resolution

#### Analog to Digital Converter (10-bit Resolution)

- 8-channel multiplexed analog data input pins (AIN0-AIN7)

- 20 µs conversion time

#### **One Channel DMA Controller**

- Supports peripheral to memory, memory to peripheral and memory to memory

- Supports single service mode and continuous service mode

#### **Clock Circuit**

- External crystal/resonator: 1 to 20 MHz

- CPU: upto 20 MHz

- USB block: 48 MHz (Generated by PLL)

- Internal ring oscillator: 32.768 kHz

#### Back-up Mode

- When V<sub>DD</sub> is lower than V<sub>LVD</sub> and LVD is "ON", the chip enters back-up mode to block oscillation and reduce the current consumption

- When reset pin is lower than Input Low Voltage (VIL), the chip enters back-up mode to block oscillation and reduce the current consumption

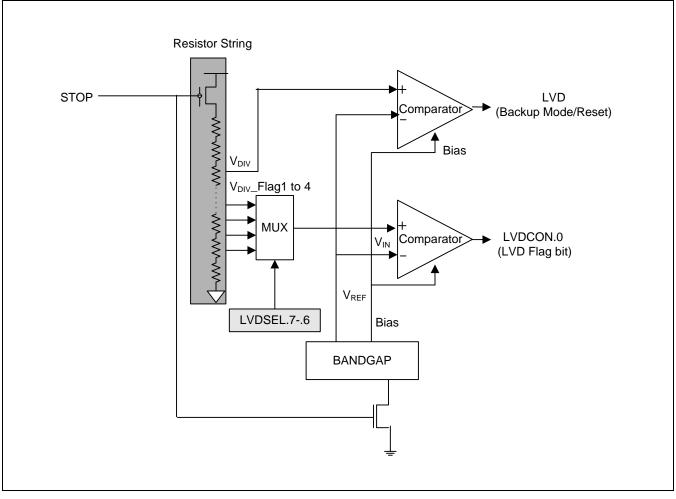

#### Low Voltage Detect Circuit

- Low voltage detect to get into back-up mode and reset

- 1.64 V (Typ.) ± 40 mV

- Low voltage detect to control LVD\_flag bit (Selectable)

- 1.90 V, 2.10 V (Typ.) ± 70 mV

- 2.30 V, 2.40 V (Typ.) ± 90 mV

- LVD-reset is enabled in the operating mode: When the voltage at VDD is falling down and passing VLVD, the chip goes into back-up mode. The voltage at VDD is rising up, the reset pulse is generated at "VDD > VLVD".

- LVD is disable in the stop mode: If the voltage at VDD is not falling down to VPOR, the reset pulse is not generated

#### **Operating Temperature Range**

• - 25 °C to + 85 °C

#### **Operating Voltage Range**

• 1.60 V to 3.6 V

#### **Operating Frequency Range**

- External crystal/resonator: 1 to 20 MHz

- USB logic: 48 MHz by PLL

- CPU: upto 20 MHz

#### Package Types

• 64-pin TQFP

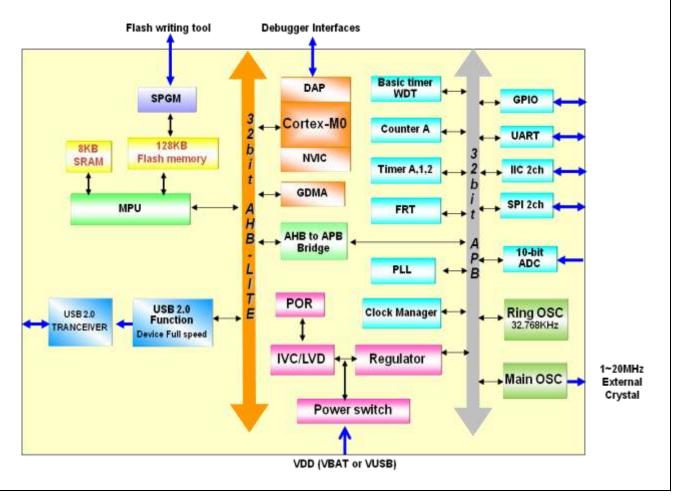

#### 1.3 Block Diagram

Figure 1-1 Block Diagram

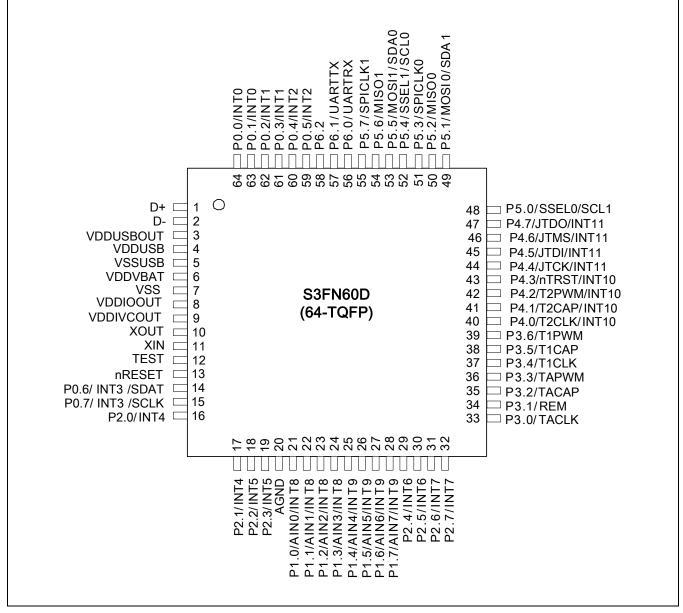

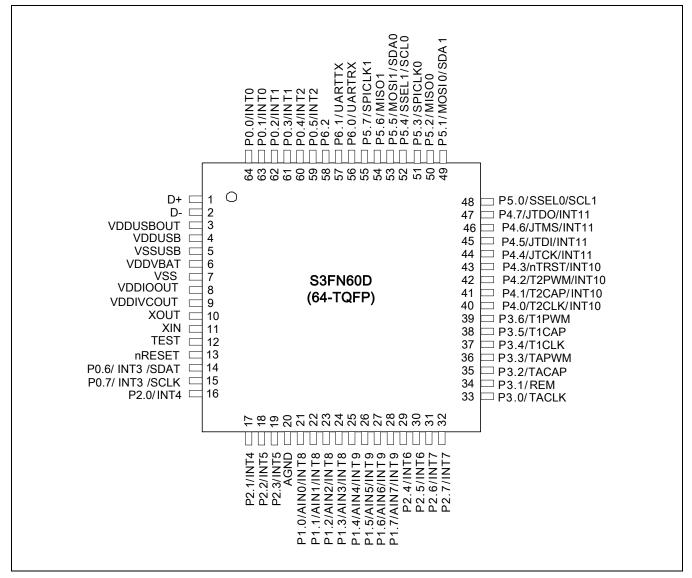

#### 1.4 Pin Assignments (64-Pin TQFP)

Figure 1-2 Pin Assignment Diagram (64-Pin TQFP Package)

| Pin<br>Names | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Circuit<br>Type | 64 Pin<br>No.  | Shared<br>Functions                                                                 |

|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-------------------------------------------------------------------------------------|

| P0.0-P0.7    | I/O         | <ul> <li>I/O port with bit-programmable pins.</li> <li>Configurable to input, output mode or n-channel open-drain output mode. Pull-up resistors can be assigned by software. Pins can be assigned individually as external interrupt inputs with noise filters, interrupt enable/ disable, falling or rising edge control.</li> <li>In the tool mode, P0.6 and P0.7 are assigned as serial MTP interface pins; SDAT and SCLK</li> </ul>                                               | 1               | 14-15<br>59-64 | Ext. INT<br>(INT0-INT3)<br>(SDAT)<br>(SCLK)                                         |

| P1.0-P1.7    | I/O         | I/O port with bit-programmable pins.<br>Configurable to input, output mode, n-<br>channel open-drain output mode or<br>alternative function mode. Pull-up resistors<br>can be assigned by software. Pins can be<br>assigned individually as external interrupt<br>inputs with noise filters, interrupt enable/<br>disable, falling or rising edge control.                                                                                                                             | 4               | 21-28          | AINO-AIN7<br>Ext.INT<br>(INT8-INT9)                                                 |

| P2.0-P2.7    | I/O         | I/O port with bit-programmable pins.<br>Configurable to input or push-pull output<br>mode, or n-channel open-drain output<br>mode. Pull-up resistors can be assigned by<br>software. Pins can be assigned individually<br>as external interrupt inputs with noise filters,<br>interrupt enable/ disable, falling or rising<br>edge control.                                                                                                                                            | 1               | 16-19<br>29-32 | Ext. INT<br>(INT4-INT7)                                                             |

| P3.0-3.6     | I/O         | <ul> <li>I/O port with bit-programmable pins.</li> <li>Configurable to input, output mode, n-<br/>channel open-drain output mode or<br/>alternative function mode. Pull-up resistors<br/>can be assigned by software.</li> <li>Port 3.1 has high current drive capability<br/>and can be assigned individually as an<br/>output pin for REM.</li> <li>P3.7 is not used.</li> </ul>                                                                                                     | 2               | 33-39          | REM<br>TOCLK, TOCAP, TOPWM<br>T1CLK, T1CAP, T1PWM                                   |

| P4.0-P4.7    | I/O         | <ul> <li>I/O port with bit-programmable pins.</li> <li>Configurable to input, output mode, n-channel open-drain output mode or alternative function mode. Pull-up resistors can be assigned by software.</li> <li>P4.3, 4, 5, 6, 7 are initially used for JTAG interface. Also P4.3, 4, 5, 6, 7 can be assigned as an I/O port from setting P4CONH/L. Pins can be assigned individually as external interrupt inputs with noise filters, interrupt enable/ disable, falling</li> </ul> | 3               | 40-47          | T2CLK, T2CAP, T2PWM<br>nTRST, JTCK, JTDI,<br>JTMS, JTDO<br>Ext.INT<br>(INT10-INT11) |

Table 1-1 Pin Descriptions of 64-TQFP

| Pin<br>Names | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                             | Circuit<br>Type | 64 Pin<br>No.                                            | Shared<br>Functions |  |

|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------|---------------------|--|

|              |             | or rising edge control.*                                                                                                                                                                                                                                                                                                                    |                 |                                                          |                     |  |

| P5.0-P5.7    | I/O         | alternative function mode. Pull-up resistors 2 48-55 M                                                                                                                                                                                                                                                                                      |                 | SDA0/1, SCL0/1<br>MOSI0/1, MISO0/1<br>SPICLK0/1, SSEL0/1 |                     |  |

| P6.0-P6.2    | I/O         | I/O port with bit-programmable pins.<br>Configurable to input, output mode, n-<br>channel open-drain output mode or<br>alternative function mode. Pull-up resistors<br>can be assigned by software.                                                                                                                                         | 2               | 56-58                                                    | 3 UARTRX<br>UARTTX  |  |

| VDDVBAT      | _           | Power supply input pin<br>It is recommended that add 0.1 $\mu$ F and<br>470uF capacitor in parallel. For application<br>systems, refer to power circuit description of<br>page 7-2.                                                                                                                                                         | _               | 6                                                        | -                   |  |

| VSS          | -           | Chip ground pin                                                                                                                                                                                                                                                                                                                             | -               | 7                                                        | -                   |  |

| AGND         | _           | ADC ground pin                                                                                                                                                                                                                                                                                                                              | -               | 20                                                       | -                   |  |

| VDDUSB       | _           | USB power supply input pin (5 V)<br>It is recommended that add 0.1 $\mu$ F and<br>10 $\mu$ F capacitor in parallel.                                                                                                                                                                                                                         | _               | 4                                                        | -                   |  |

| VSSUSB       | -           | USB ground pin                                                                                                                                                                                                                                                                                                                              | _               | 5                                                        | -                   |  |

| XOUT, XIN    | _           | System clock input and output pins                                                                                                                                                                                                                                                                                                          | -               | 10, 11                                                   | -                   |  |

| TEST         | I           | Test signal input pin       If on board programming is needed, It is         If on board programming is needed, It is       recommended that add 0.1 μF capacitor for         better noise immunity; otherwise, connect       -         TEST pin to VSS directly. There is internal       1         pull-down resistor in TEST pin.       - |                 | 12                                                       | _                   |  |

| nRESET       | I           | System reset signal input pin and back-up<br>mode input.It is recommended that add a 0.1 μF<br>capacitor between nRESET pin and VSS513for better noise immunity. There is internal<br>pull-up resistor in nRESET pin that is active<br>low.513                                                                                              |                 | 13                                                       | -                   |  |

| VDDIVCOUT    | _           | Connected to GND through capacitor.It is recommended that add a 1 μF-9                                                                                                                                                                                                                                                                      |                 | _                                                        |                     |  |

| VDDUSBOUT    | _           | Connected to GND through capacitor It is recommended that add a 2.2 $\mu$ F capacitor.                                                                                                                                                                                                                                                      |                 |                                                          | -                   |  |

| Pin<br>Names | Pin<br>Type | Pin Description                                                                        | Circuit<br>Type | 64 Pin<br>No. | Shared<br>Functions |

|--------------|-------------|----------------------------------------------------------------------------------------|-----------------|---------------|---------------------|

| VDDIOOUT     | _           | Connected to GND through capacitor It is recommended that add a 4.7 $\mu$ F capacitor. | _               | 8             | -                   |

| D +          | I           | USB signal pin                                                                         | _               | 1             | _                   |

| D –          | Ι           | USB signal pin                                                                         | -               | 2             | _                   |

| nTRST        | Ι           | JTAG test reset input                                                                  | 3               | 43            | I/O port            |

| JTCK         | Ι           | JTAG test clock input                                                                  | 3               | 44            | I/O port            |

| JTDI         | I           | JTAG test data input                                                                   | 3               | 45            | I/O port            |

| JTMS         | Ι           | JTAG test mode selection input                                                         | 3               | 46            | I/O port            |

| JTDO         | 0           | JTAG test data output                                                                  | 3               | 47            | I/O port            |

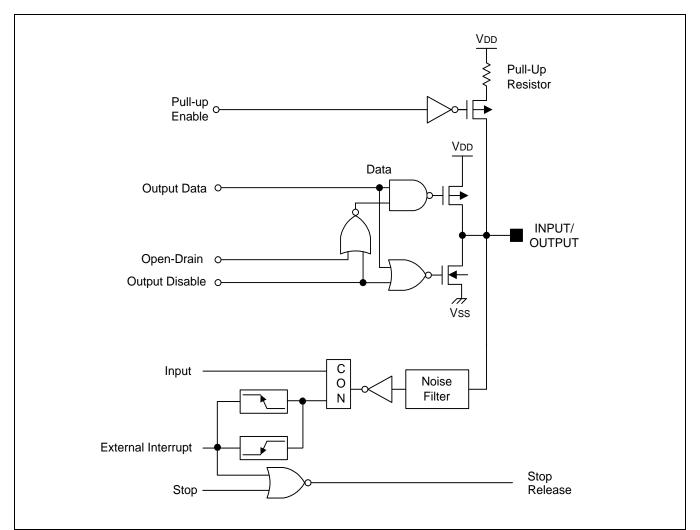

#### 1.5 Pin Circuits

Figure 1-3 External Interrupt Port to Wake Up Stop Mode (Pin Circuit Type 1)

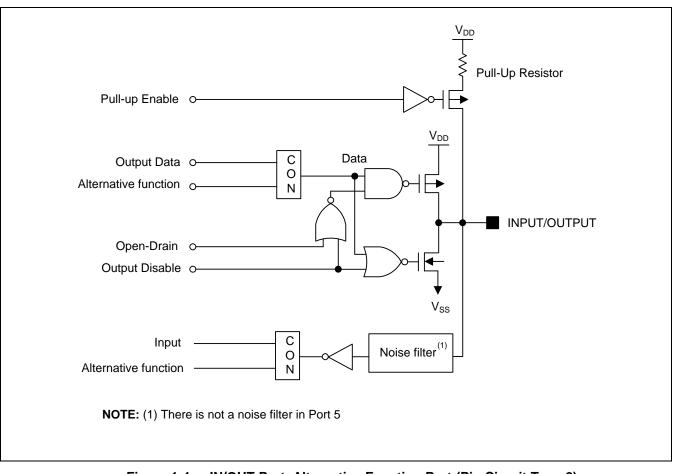

Figure 1-5 IN/OUT Port, Alternative Function Port & Ext. Interrupt (Pin Circuit Type 3)

Figure 1-6 IN/OUT Port, Alternative Input Port (ADC) & Ext. Interrupt (Pin Circuit Type 4)

Figure 1-7 nRESET Pin (Pin Circuit Type 5)

|  |  |  | • |  |  |

|--|--|--|---|--|--|

|  |  |  | • |  |  |

|  |  |  | • |  |  |

|  |  |  | • |  |  |

|  |  |  | • |  |  |

|  |  |  | • |  |  |

|  |  |  | ٠ |  |  |

|  |  |  | ٠ |  |  |

|  |  |  |   |  |  |

|  |  |  |   |  |  |

|  |  |  |   |  |  |

#### 2.1 Overview

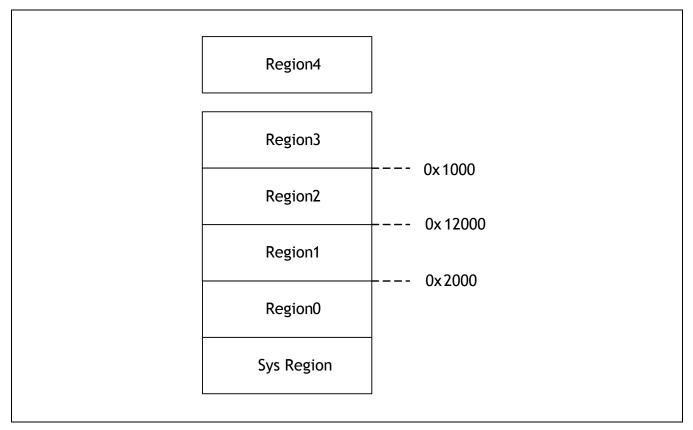

#### 2.2 Memory Configuration in Cortex M0 Side

- Program Memory:

- 128 Kbyte internal program flash (ROM)

- Data Memory:

- 8 Kbyte internal data memory (SRAM)

Figure 2-1 Program Memory Configuration

SAMSUNG ELECTRONICS

#### 2.3 Smart Option

Smart option is the program memory option for starting condition of the chip. The program memory addresses used by smart option is 00C0H. The default value of smart option bits in program memory is 0FFH. Before execution the program memory code, user can set the smart option bits according to the hardware option for user to want to select.

| Name              | Bit     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSVD              | [31:29] | RW   | Reserved (Not used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BTCLK             | [28:26] | RW   | Reset value of basic timer clock (BTCON.4 .3 .2) selection bit<br>000= fosc/2<br>001= fosc/4<br>010= fosc/16<br>011= fosc/32<br>100= fosc/128<br>101= fosc/256<br>110= fosc/1024<br>111= fosc/2048                                                                                                                                                                                                                                                                                               |

| WDT               | [25]    | RW   | WDT enable/disable bit<br>0 = WDT is disabled<br>1 = WDT is enabled                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RSVD              | [24:22] | RW   | Reserved (Not used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

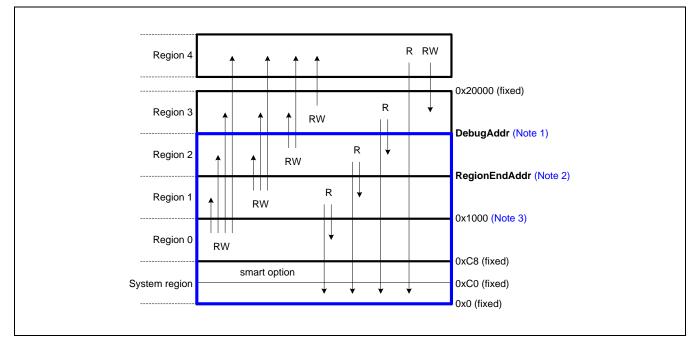

| RegionOption      | [21]    | RW   | Usable region selection bit<br>0 = Use from region 0 to region 2<br>1 = Use from region 0 to region 3                                                                                                                                                                                                                                                                                                                                                                                            |

| Debug             | [20]    | RW   | <ul> <li>Debug &amp; MPU enable/disable bit</li> <li>0 = Debug mode is disabled and MPU is enabled</li> <li>Flash read/write no accessible. Flash will be read 0xBF00H that is NOP instruction. Flash write instructions will be not operated</li> <li>MPU is enabled. User code cannot change MPU enable/disable control bit.</li> <li>1 = Debug mode is enabled and MPU is disabled</li> <li>Flash read/write accessible</li> <li>MPU is disabled. User code can control MPU block.</li> </ul> |

| DebugAddr         | [19:10] | RW   | Protected debug region address<br>Debug region end address bits<br>[17:0] = A17 to A0 (128 Kbyte region)<br>Debug region start/end address is located in<br>0x0000_00C8H(fixed) ≤ DebugAddr<[17:0]<br>NOTE: When debug bit is only set to "0", debug region address is active for<br>protecting debug mode                                                                                                                                                                                       |

| RegionEndAd<br>dr | [9:0]   | RW   | Region end address of MPU SFR<br>RegionEndAddr[8:0] = A17 to A8<br>: Although flash memory 256Kbyte range have A17 to A0 address bits, A9 to<br>A0 is not used<br>If RegionOption is set to 0: This address is set to MPU region1 end register                                                                                                                                                                                                                                                   |

| Name | Bit | Туре | Description                                                                  |  |

|------|-----|------|------------------------------------------------------------------------------|--|

|      |     |      | If RegionOption is set to 1: This address is set to MPU region2 end register |  |

#### NOTE:

- 1. The default value of smart option bits in program memory is 0xFFFF\_FFFH

- 2. After CPU operation resumes (BTCNT.5 set), basic timer clock selection bits and watchdog timer enable selection bits can be changed by s/w (Refer to 10-5 page BTCON)

|  | • |  |

|--|---|--|

|  | • |  |

|  | • |  |

|  | • |  |

|  | • |  |

#### 3.1 Overview

The Cortex-M0 processor is a very low gate count, highly energy efficient processor that is intended for microcontroller and deeply embedded applications that require an area optimized processor.

#### 3.2 Features

The Processor Features and Benefits are:

- Tight integration of system peripherals reduces area and development costs

- Thumb instruction set combines high code density with 32-bit performance

- Power control optimization of system components

- Integrated sleep modes for low power consumption

- Fast code execution permits slower processor clock or increases sleep mode time

- Hardware multiplier (1 cycle multiplier)

- Deterministic, high-performance interrupt handling for time-critical applications

- Serial wire debug reduces the number of pins required for debugging

- ARM architecture

- The Nested Vectored Interrupt Controller (NVIC), Debug and processor are implementations of the ARMv6-M architecture profile. See the ARMv6-M ARM

#### 3.3 Interfaces

The interfaces included in the processor for external access include:

- External AHB-lite interface

- Debug Access Port (DAP)

For information about cortex-M0 architectural, see the cortex-M0 technical reference manual or <u>www.arm.com</u>.

|  | • |  |

|--|---|--|

|  | • |  |

# 4.1 Overview

The NVIC and Cortex-M0 processor enable low latency interrupt processing and provide efficient service for late arriving interrupts. There are 32 individual interrupt vector sources including 16 cortex-M0 own interrupt sources.

# 4.2 Features

- Cortex-M0's NVIC interface

- 32 interrupt vector sources (not including 16 cortex-M0 own interrupt vector sources)

- Low latency exception and interrupt handling

- Power management control

- Implement cortex-M0 system control registers

The NVIC and the processor core interface are closely coupled, which enables low latency interrupt processing and efficient processing of late arriving interrupts. All interrupts including the core exceptions are managed by the NVIC. For more information on exceptions and NVIC programming, see ARMv6-M ARM Manual.

# 4.3 Interrupt Sources & Interrupt Vector

Interrupt vector table includes Cortex-M0's processor interrupt vectors and vectors for S3FN60D interrupt sources.

| Vector Category         | Address                          | Vector                | Description                                                                       |

|-------------------------|----------------------------------|-----------------------|-----------------------------------------------------------------------------------|

|                         | 0x0000_0000                      | Reserved              | Starting value of the MSP                                                         |

|                         | 0x0000_0004                      | Reset                 | _                                                                                 |

|                         | 0x0000_0008                      | NMI                   | Non-maskable interrupt                                                            |

|                         | 0x0000_000C Ha                   |                       | All class of fault                                                                |

|                         | 0x0000_0010                      | MemManage             | Memory management fault                                                           |

|                         | 0x0000_0014                      | BusFault              | Pre-fetch fault, memory access fault                                              |

|                         | 0x0000_0018                      | UsageFault            | Undefined instruction or illegal state                                            |

| Coro Interrupt Vector   | 0x0000_001C                      | Reserved              | -                                                                                 |

| Core Interrupt Vector   | 0x0000_0020                      | Reserved              | -                                                                                 |

|                         | 0x0000_0024                      | Reserved              | _                                                                                 |

|                         | 0x0000_0028                      | Reserved              | _                                                                                 |

|                         | 0x0000_002C                      | SVCall                | System service call via SWI instruction                                           |

|                         | 0x0000_0030                      | Debug Monitor         | Debug monitor                                                                     |

|                         | 0x0000_0034                      | Reserved              | _                                                                                 |

|                         | 0x0000_0038                      | PendSV                | Pendable request for system service                                               |

|                         | 0x0000_003C                      | SysTick               | System tick timer                                                                 |

| System Interrupt Vector | 0x0000_0040<br>to<br>0x0000_00C0 | INTV0<br>to<br>INTV31 | Vectors for interrupt sources generated by peripherals and external input signals |

| Table 4-1 | <b>Core Exception Vector</b> |

|-----------|------------------------------|

|-----------|------------------------------|

# 4.4 System Interrupt Vector

| Table 4-2 System Interrupt Vectors & Sources |

|----------------------------------------------|

|----------------------------------------------|

| Number | Address     | Vector     | Description                                |

|--------|-------------|------------|--------------------------------------------|

| 0      | 0x0000_0040 | MPUINT     | MPU abort                                  |

| 1      | 0x0000_0044 | TAINT      | Timer A P_END/MATCH/OVERFLOW/CAPTURE       |

| 2      | 0x0000_0048 | T1INT      | Timer 1 P_END/MATCH/OVERFLOW/CAPTURE       |

| 3      | 0x0000_004C | SPI0INT    | SPI0 interrupt                             |

| 4      | 0x0000_0050 | SPI1INT    | SPI1 interrupt                             |

| 5      | 0x0000_0054 | I2C0INT    | I2C0 interrupt                             |

| 6      | 0x0000_0058 | I2C1INT    | I2C1 interrupt                             |

| 7      | 0x0000_005C | BTOVF      | Basic timer overflow                       |

| 8      | 0x0000_0060 | ADC_INT    | ADC interrupt                              |

| 9      | 0x0000_0064 | UARTTXINT  | UART data transmit interrupt               |

| 10     | 0x0000_0068 | UARTRXINT  | UART data receive interrupt                |

| 11     | 0x0000_006C | UARTERRINT | UART data error interrupt                  |

| 12     | 0x0000_0070 | T2INT      | Timer 2 P_END/MATCH/OVERFLOW/CAPTURE       |

| 13     | 0x0000_0074 | FRTINT     | FRT MATCH                                  |

| 14     | 0x0000_0078 | DMAINT     | DMA interrupt                              |

| 15     | 0x0000_007C | VUSB_DET   | VUSB detect                                |

| 16     | 0x0000_0080 | INT0       | External pin interrupt P0.0/P0.1           |

| 17     | 0x0000_0084 | INT1       | External pin interrupt P0.2/P0.3           |

| 18     | 0x0000_0088 | INT2       | External pin interrupt P0.4/P0.5           |

| 19     | 0x0000_008C | INT3       | External pin interrupt P0.6/P0.7           |

| 20     | 0x0000_0090 | INT4       | External pin interrupt P2.0/P2.1           |

| 21     | 0x0000_0094 | INT5       | External pin interrupt P2.2/P2.3           |

| 22     | 0x0000_0098 | INT6       | External pin interrupt P2.4/P2.5           |

| 23     | 0x0000_009C | INT7       | External pin interrupt P2.6/P2.7           |

| 24     | 0x0000_00A0 | INT8       | External pin interrupt P1.0/P1.1/P1.2/P1.3 |

| 25     | 0x0000_00A4 | INT9       | External pin interrupt P1.4/P1.5/P1.6/P1.7 |

| 26     | 0x0000_00A8 | INT10      | External pin interrupt P4.0/P4.1/P4.2/P4.3 |

| 27     | 0x0000_00AC | INT11      | External pin interrupt P4.4/P4.5/P4.6/P4.7 |

| 28     | 0x0000_00B0 | CAINT      | Counter A interrupt                        |

| 29     | 0x0000_00B4 | USBINT     | USB Resume/Suspend/Reset interrupt         |

| 30     | 0x0000_00B8 | USBSOF     | USB SOF interrupt                          |

| 31     | 0x0000_00BC | USBEP      | USB Endpoint 0/1/2/3/ interrupt            |

### NOTE:

- 1. Interrupt mask and pending status are controlled to SFR of each peripherals.

- 2. All interrupts vectors are controlled to NVIC of Cortex-M0. (Please refer to Cortex-M0 NVIC manual for details) The control registers of NVIC can control all interrupts.

|  | • |  |

|--|---|--|

|  | • |  |

|  | • |  |

|  | • |  |

|  | • |  |

|  | • |  |

# 5 Memory Map

# 5.1 Overview

To support the control of peripheral hardware, the address for peripheral control registers are memory-mapped to the area higher than 0x4010\_0FFFH. Memory mapping lets you use a mnemonic as the operand of an instruction in place of the specific memory location.